关于SRAM与DRAM及其容量扩展

简单介绍静态和动态的随机存取存储器,以及如何将其扩展成更大容量的存储器

关于SRAM与DRAM及其容量扩展

一、SRAM

内存分为RAM和ROM,RAM又分为SRAM和DRAM

1.1 SRAM的优缺点

- 静态随机存取存储器(Static Random-Access Memory)中二进制数据使用传统的触发器(Flip Flop)逻辑门电路进行存储

- 优点:存取速度快(静态的比动态的快,类比静态链接库

.lib比动态链接库.dll快) - 缺点:集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,因此SRAM的成本也会更高(同样面积的硅片可以做出更大容量的DRAM)

- 优点:存取速度快(静态的比动态的快,类比静态链接库

1.2 SRAM单元

1.2.1 锁存器

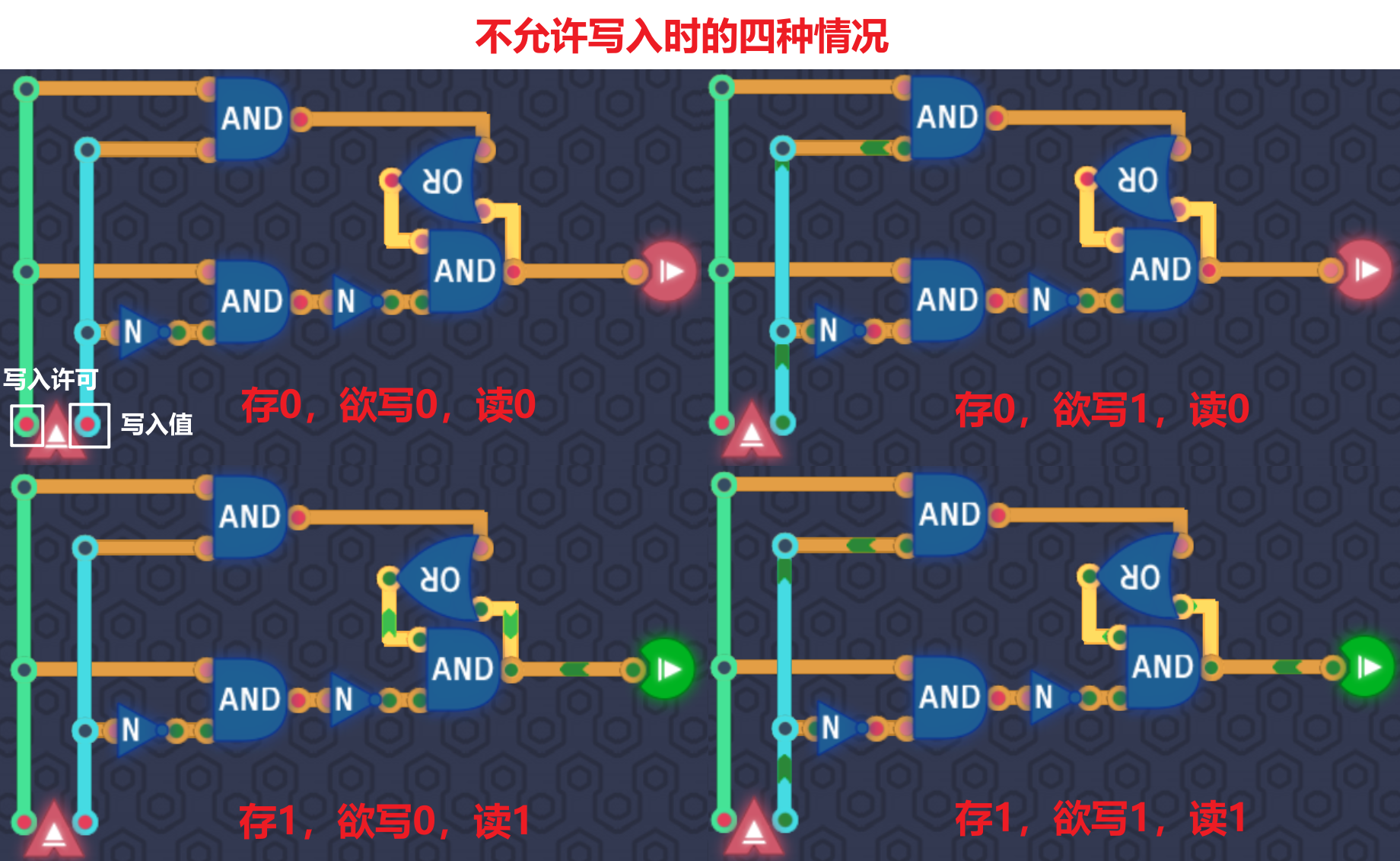

- 锁存器(Latch)在非写入时的四种状态如下所示

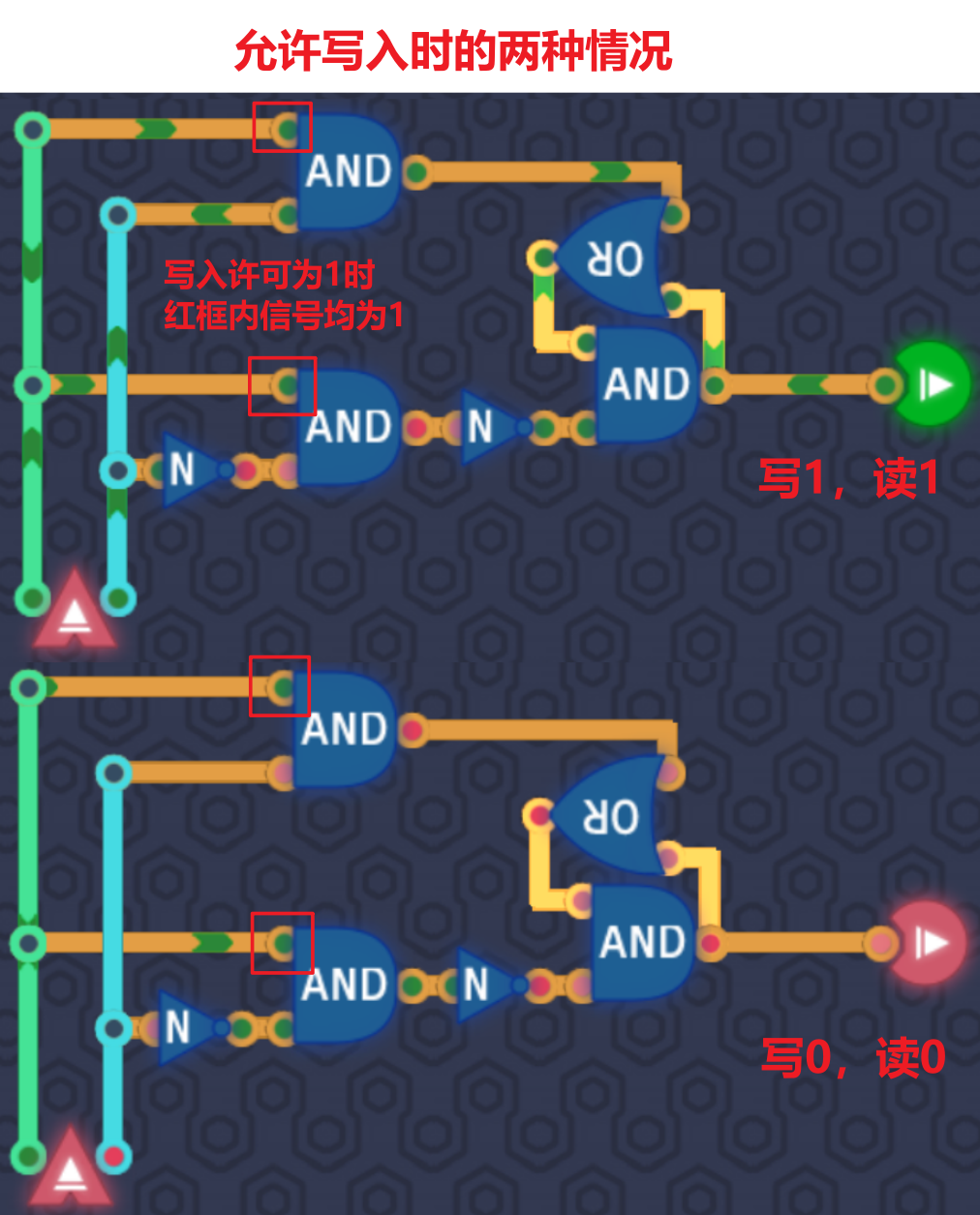

- 锁存器的写,第二个输入信号即写入值信号,右侧与门即为锁存器存储的值(永远输出存储值)

- 若写入值为

1,则使得上方与门激活,从而激活右侧或门,从而激活右侧与门 - 若写入值为

0,则使得下方与门激活,从而通过其右侧非门使得右侧与门失活

- 若写入值为

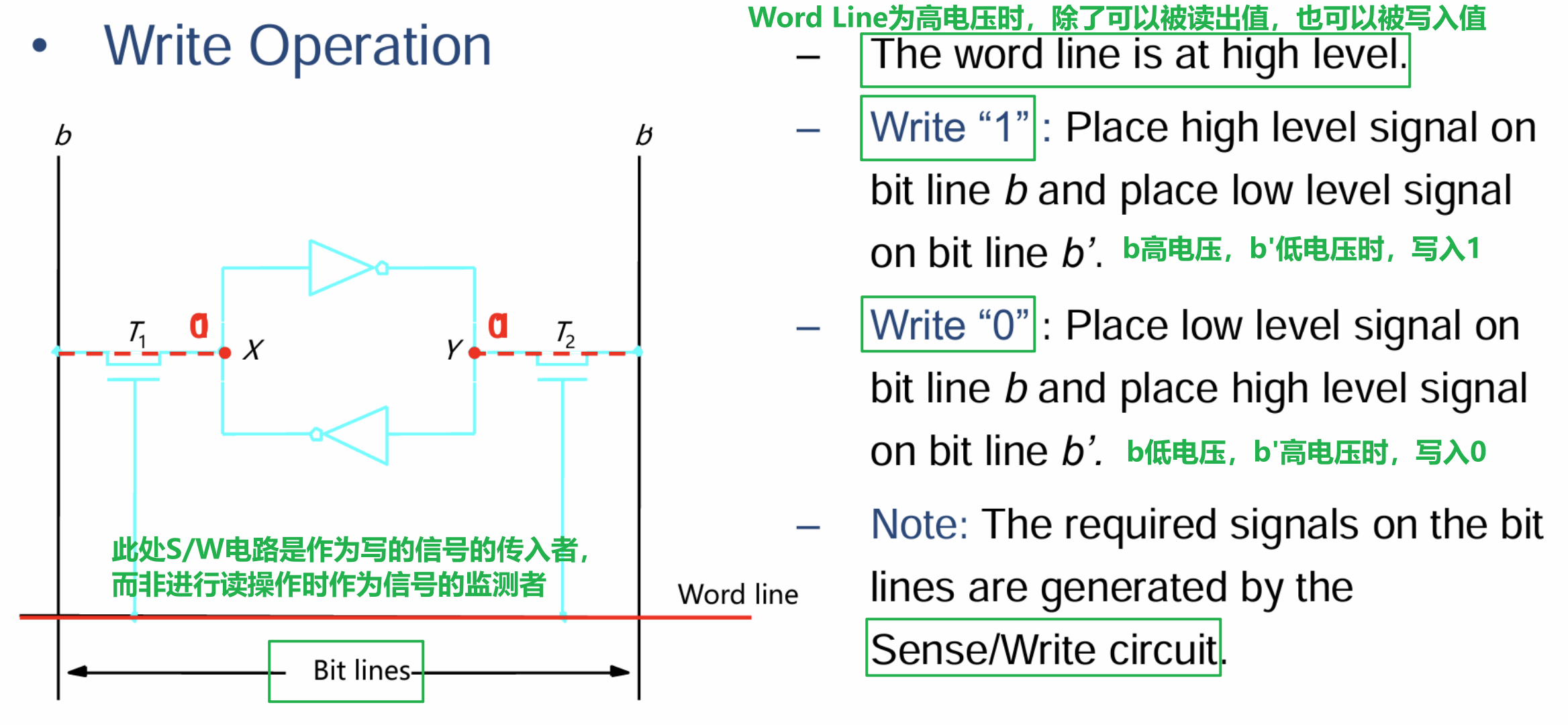

1.2.2 SRAM单元一般实现

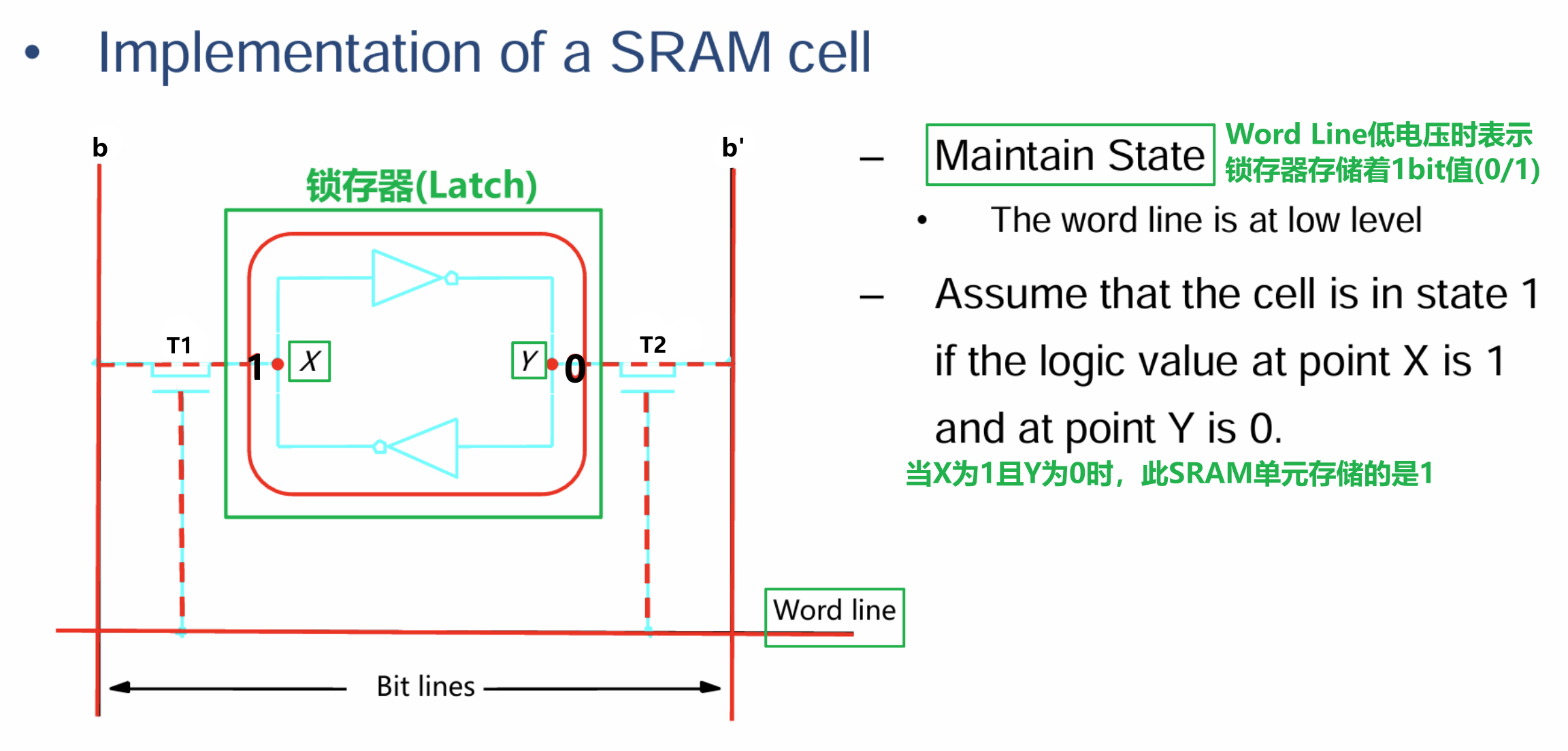

- 下面是一个SRAM单元(Cell)的结构示意,每个该单元存储着一位数据的值(0/1)

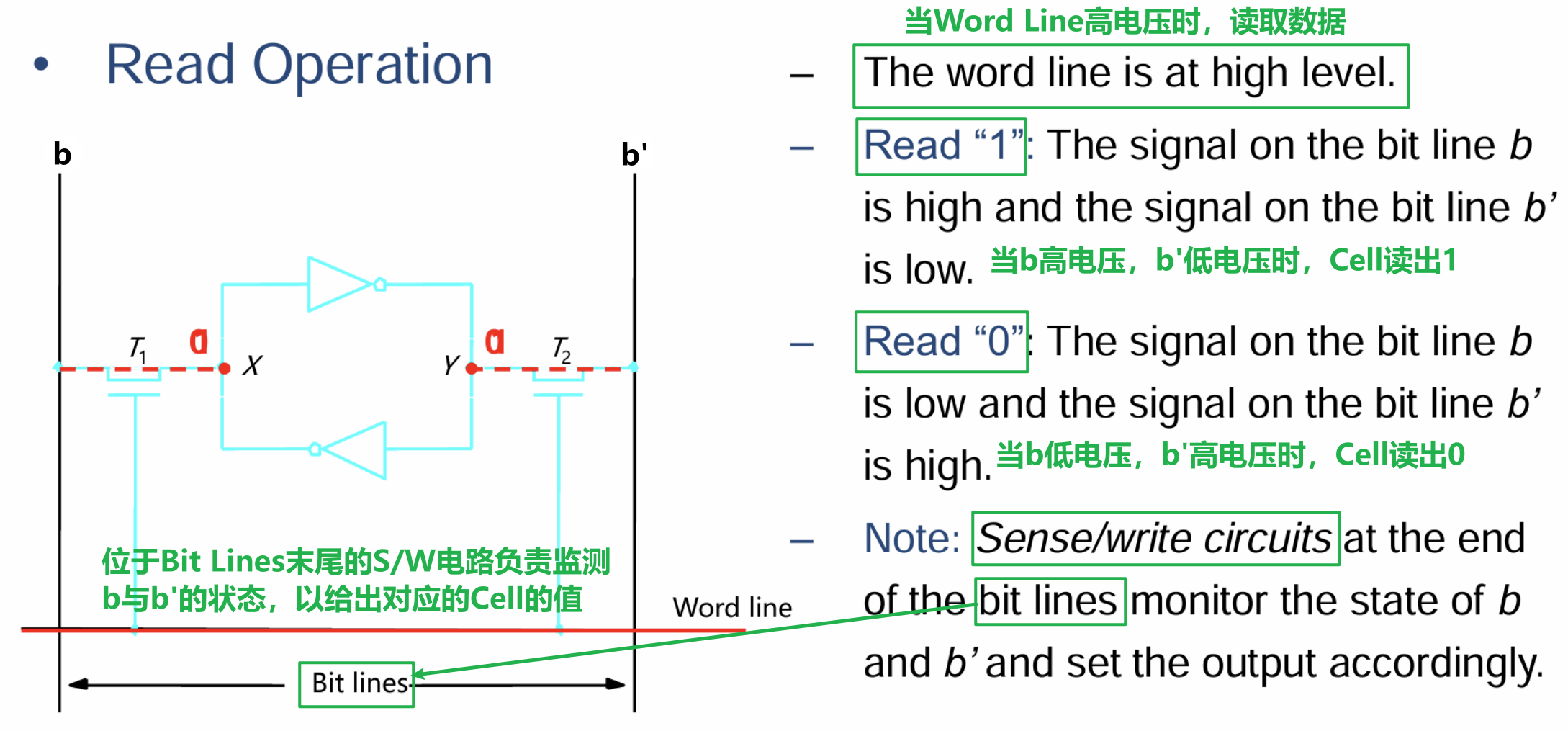

- 下方两图展示了该SRAM单元格的值是如何被读取、写入的

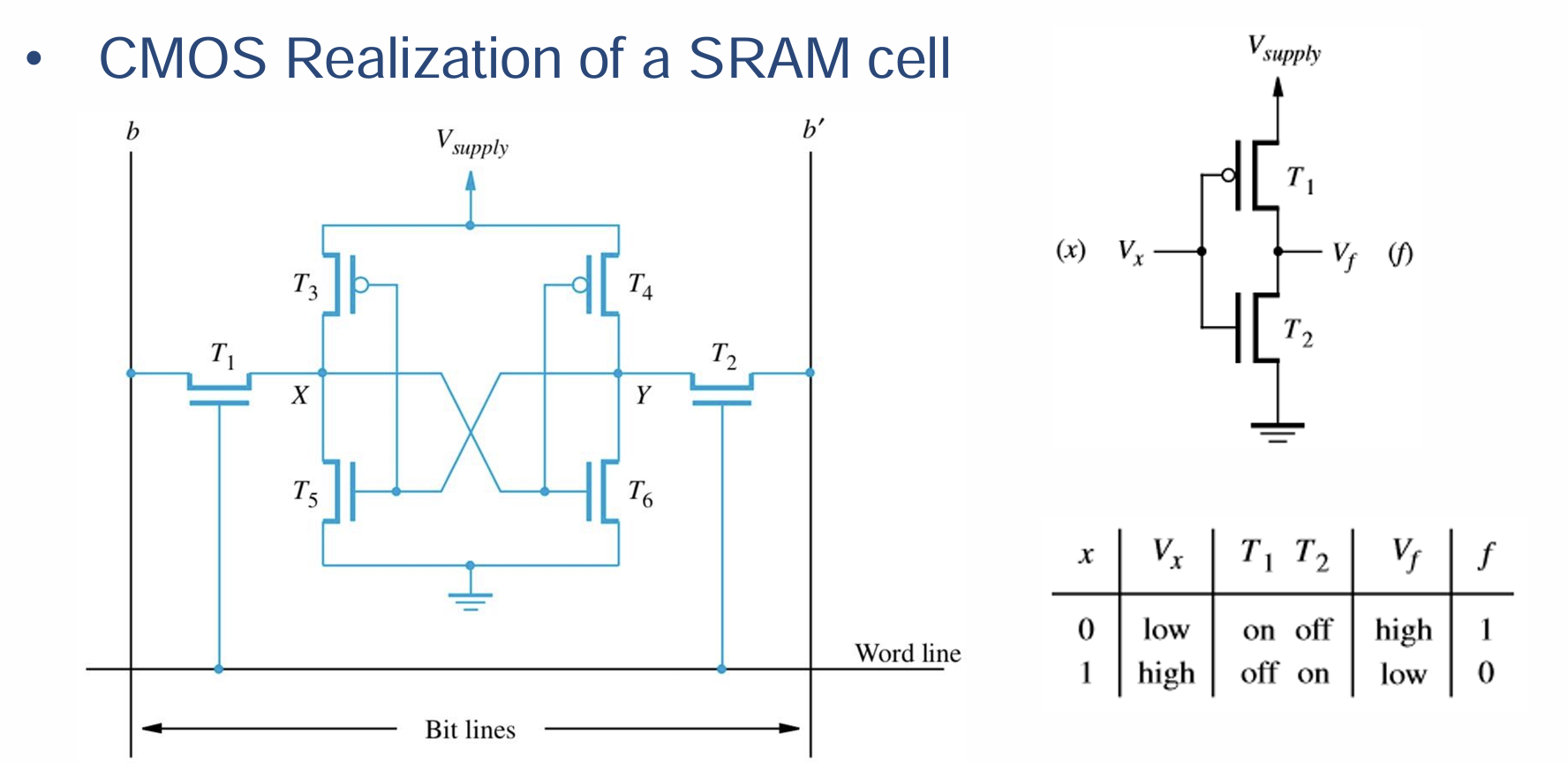

1.2.3 SRAM单元的CMOS实现

- CMOS实现的SRAM单元的能耗(Power Consumption)低

- The power supply voltage is 5V in older CMOS SRAMs or 3.3V in new low-voltage versions

- If power is interrupted and then it is restored, the latch will settle into a stable state, but it will not necessarily be the same state the cell was in before the interruption

1.3 SRAM芯片

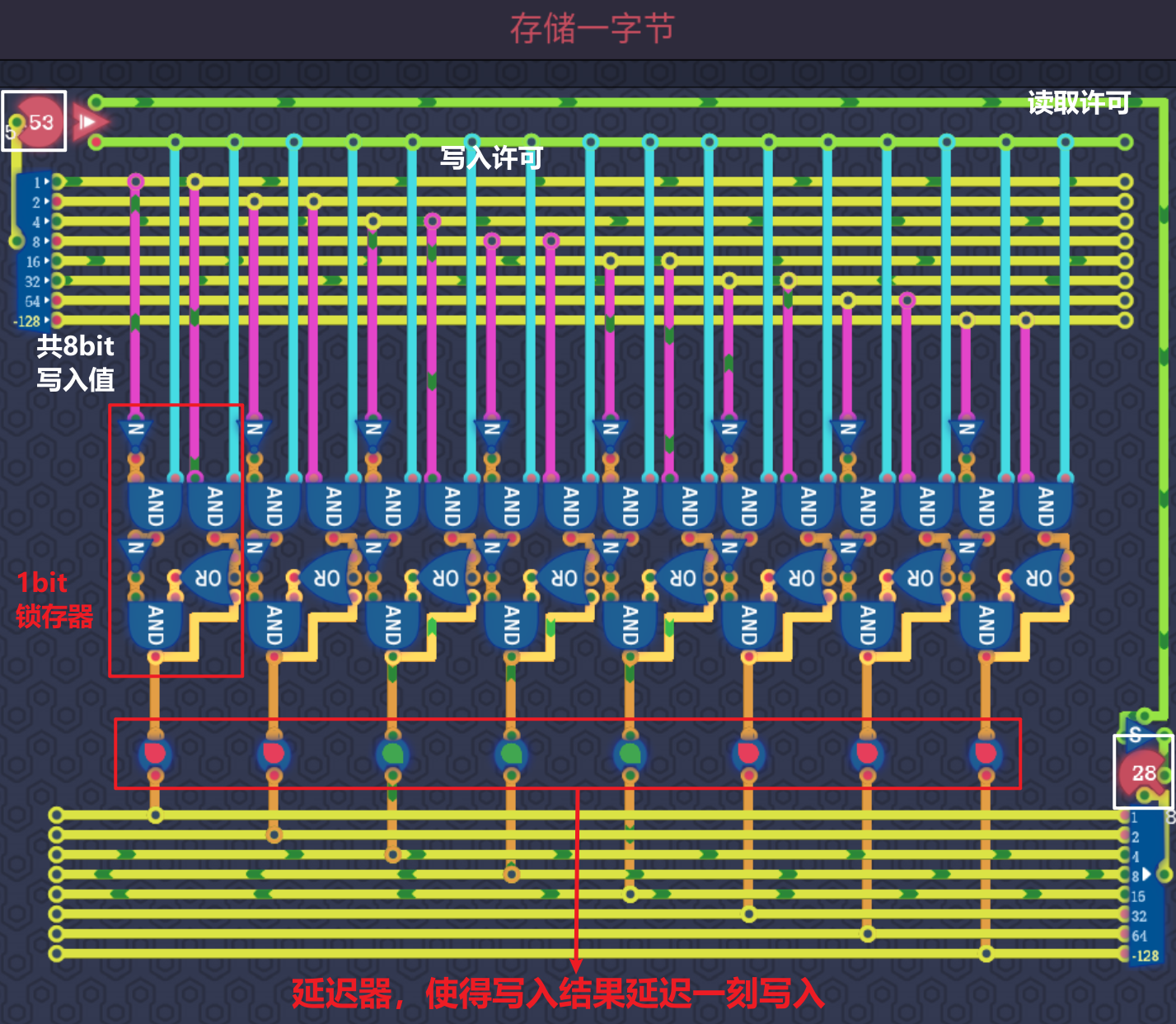

1.3.1 多位存储器

- 之前我们介绍了可以存储1bit数据的锁存器的原理,我们可以进一步利用8个锁存器来制造一个存储8bit数据的存储器(8位寄存器),以此类推

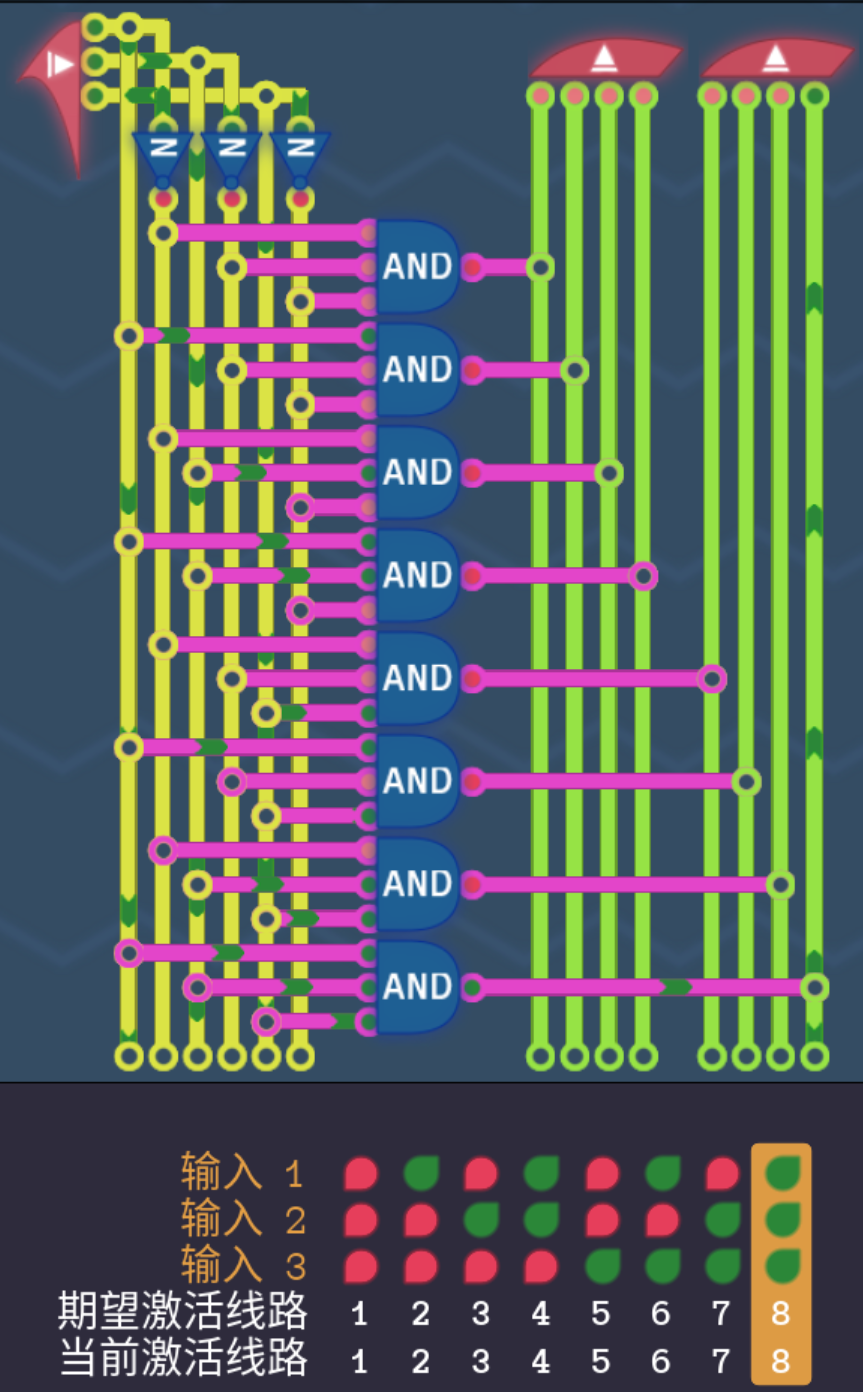

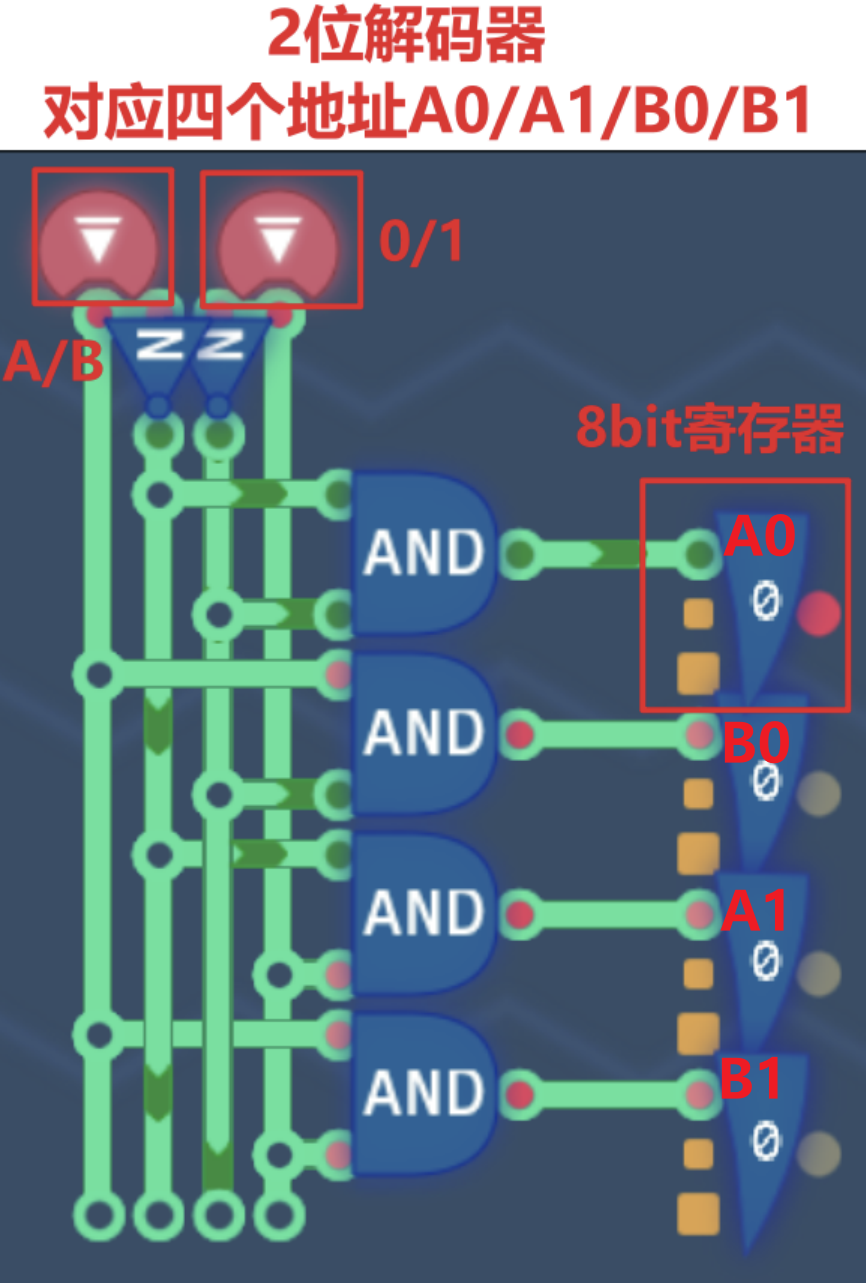

1.3.2 多位解码器

- 解码器(Decoder)就是通过传入的$n$位地址来锁定$2^n$个位置中的某一个的,1bit的数据可以代表两种状态,即两种地址

- 3bit的解码器(3bit数据对应$2^3=8$种不同的地址)如下所示

1.3.3 统合解码器与存储器

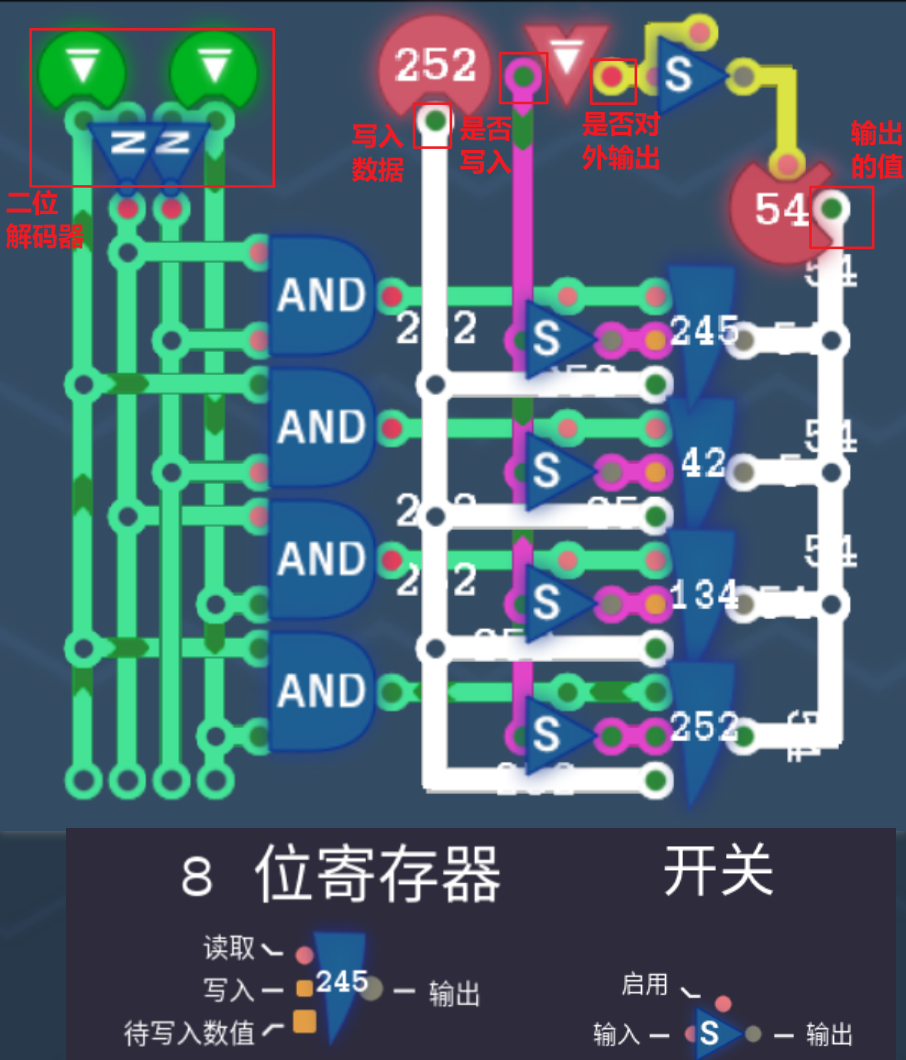

- 将存储器与解码器组合起来,就变成了内存芯片,下面我们以组合4个8bit寄存器为例

- 我们需要4个地址来分别访问这四个字节的数据,也就是说我们需要一个2位解码器

- 最终结合其它部分,我们就得到了一个

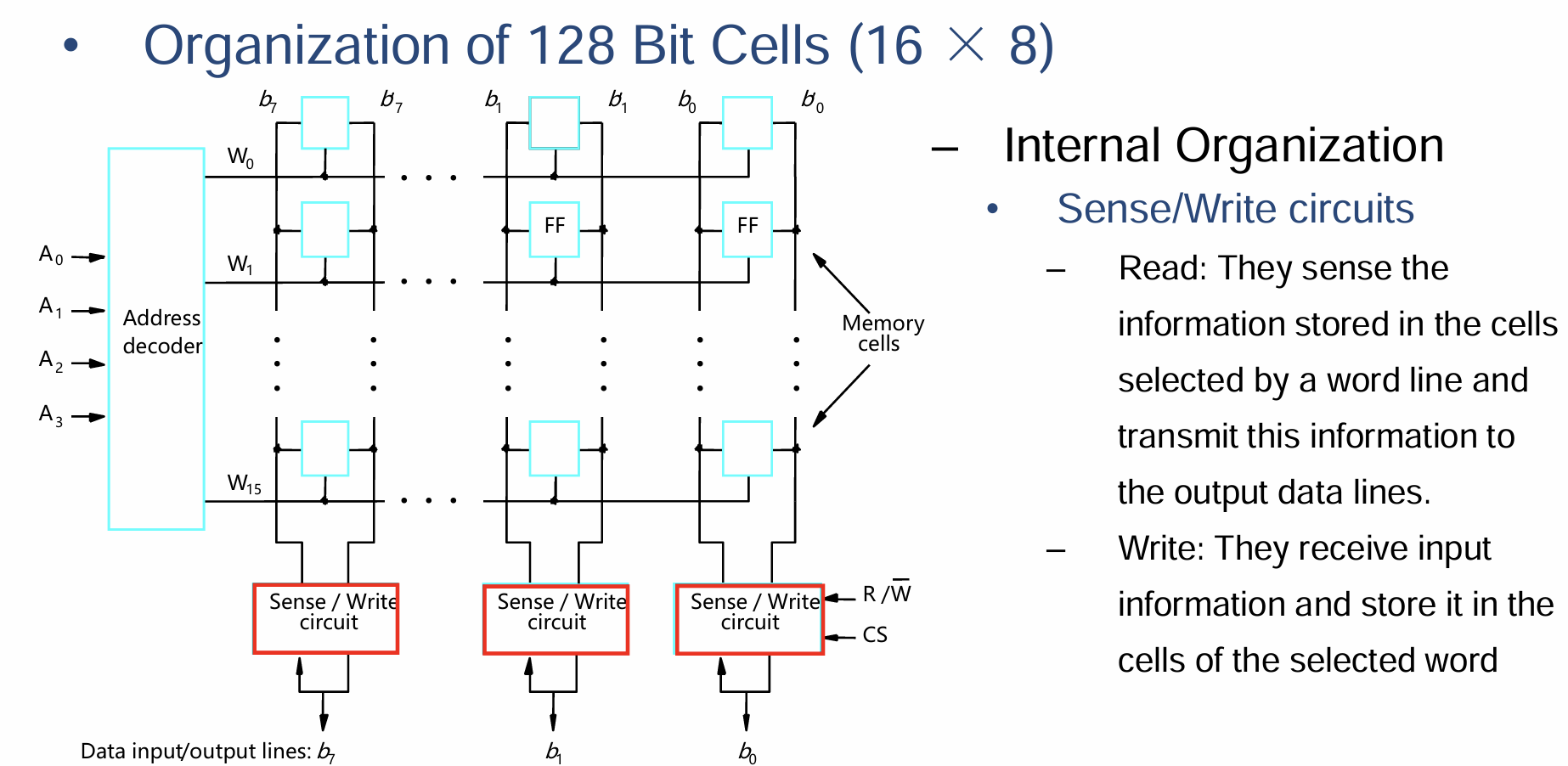

1.3.3 SRAM芯片组织结构

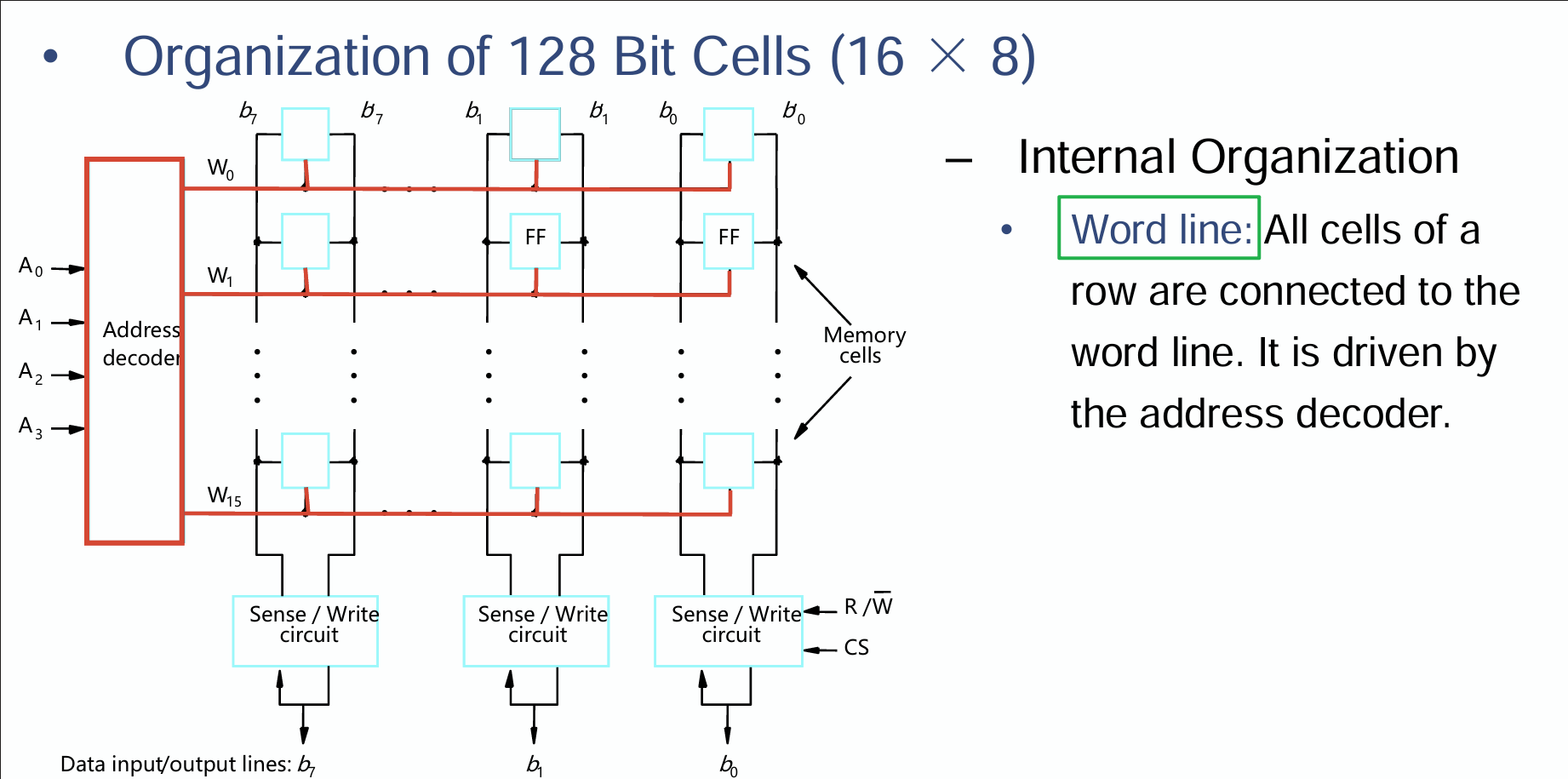

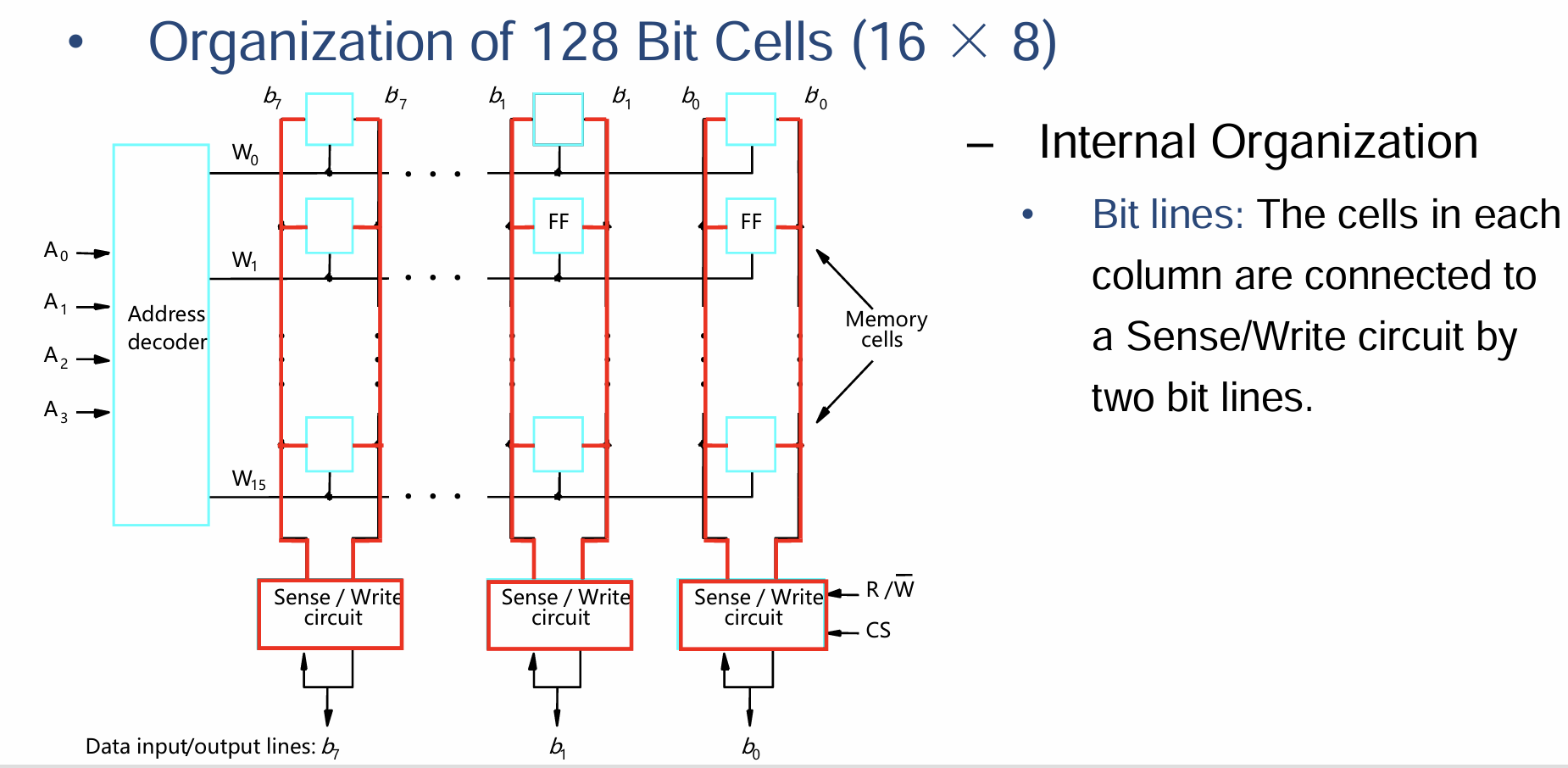

- 16x8(字数x位数)位的SRAM芯片存储着16个字长为8比特(1字节)的字,也就是说每个字由8横着的个SRAM单元组成,每个字以竖向进行排列

- 外界对这块SRAM芯片进行访问时,有16种块地址(字)可以选择

- 下图左侧的一组$A_i$就是以4位二进制数的组合,表示$16=2^4$个字地址之一,以进行寻址

- Word Line(共16根,用于遍历每行的比特)如下红线所示,其电压高低决定是否存在读写操作

- Bit Line(共8对,用于遍历每列,即所有共16行字的每个比特数据)如下,用于直接反映或修改SRAM单元存储的比特值

- Sense/Write电路(共8个)如下,其位于Bit Line末端,用于对b与b’两线的电压信号进行读取或传入,以间接读取或修改SRAM单元存储的比特值

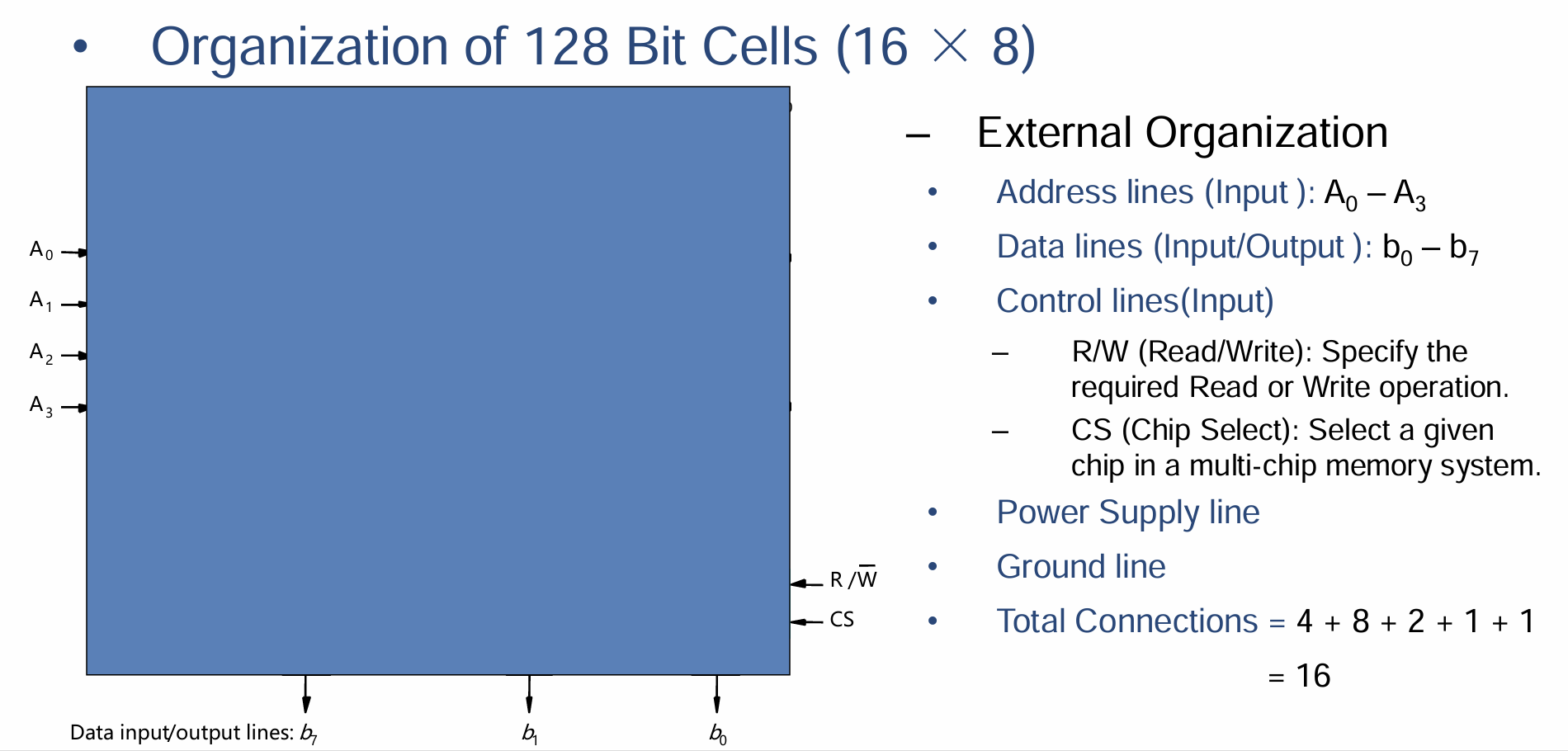

- 该16x8位的SRAM芯片的外部组织结构如下

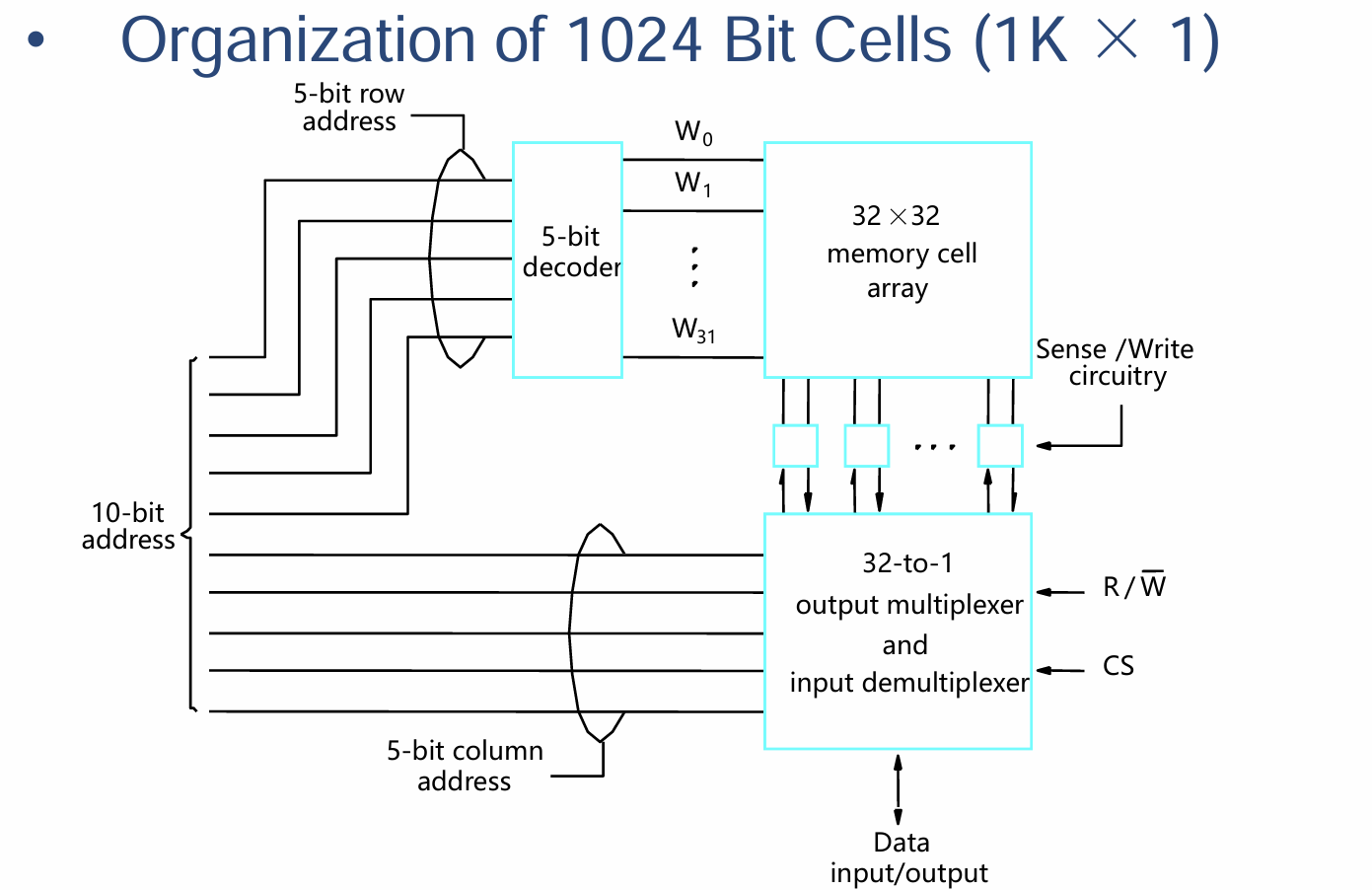

- 更大规模的SRAM芯片的组织结构如下,可以通过10位bit数组合(1K是单位,指1024而不是一千)对该SRAM芯片进行寻址

二、DRAM

2.1 DRAM的优缺点

- 动态随机存取存储器(Dynamic Random-Access Memory)与SRAM的优缺点相反互补

- 密度高,成本低

- 访问速度慢,不访问其还会漏电(电容漏电,所以需要周期性刷新)

2.2 DRAM单元的一般实现

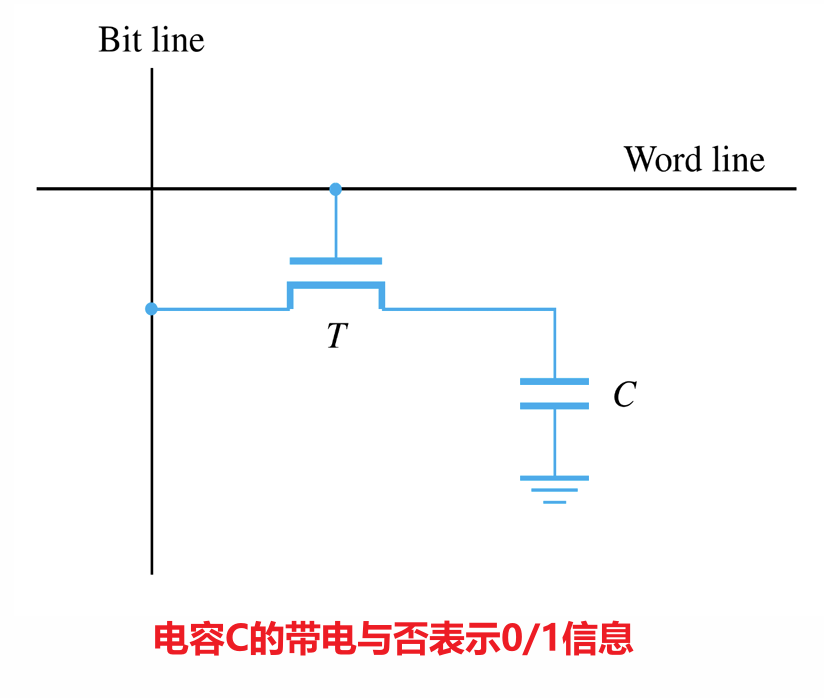

- 动态随机存取存储器(Dynamic Random-Access Memory)中,数据中的每一位(bit)的值使用电容的带电与否来表示,带电表示1,不带电表示0

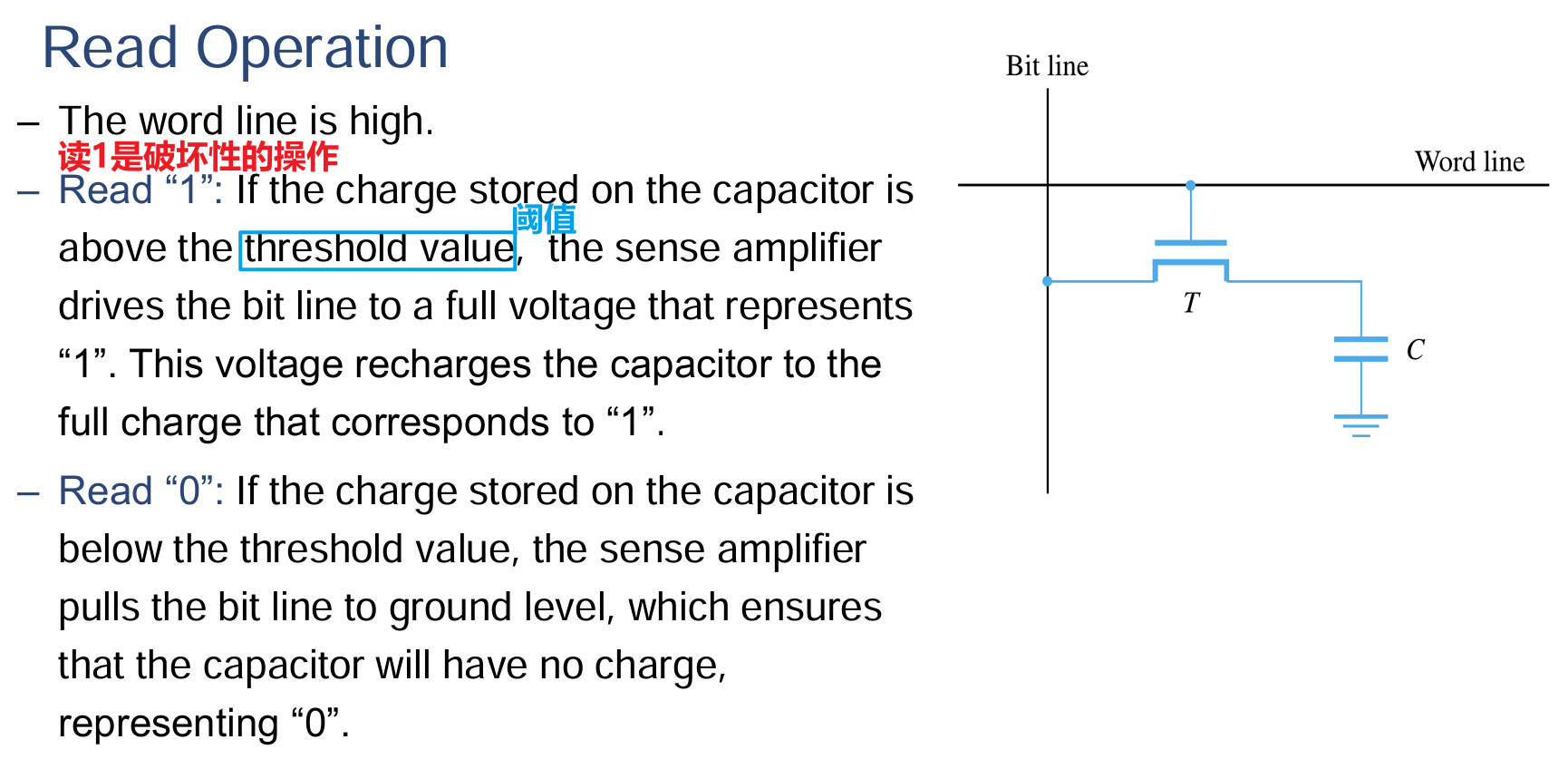

- DRAM单元进行读取操作

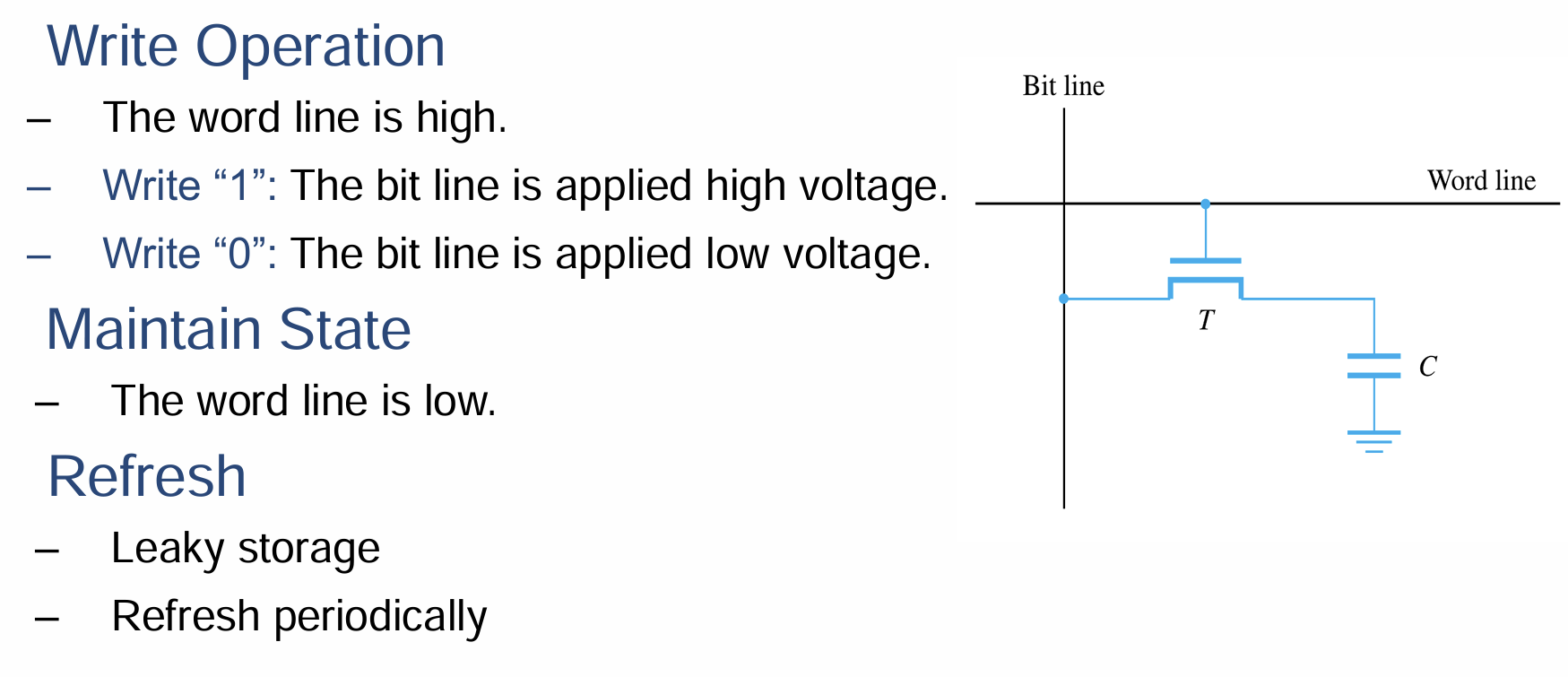

- DRAM单元的写入、信息保持、周期性刷新(读一遍即可刷新,0不变,1被读完后就会)

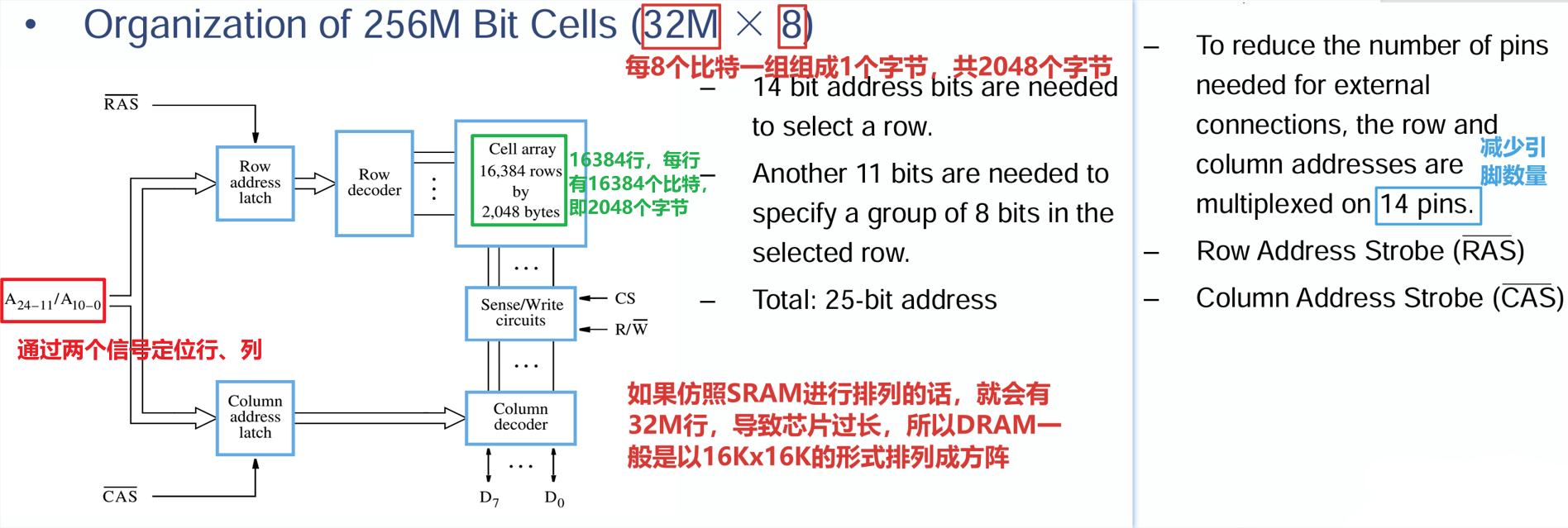

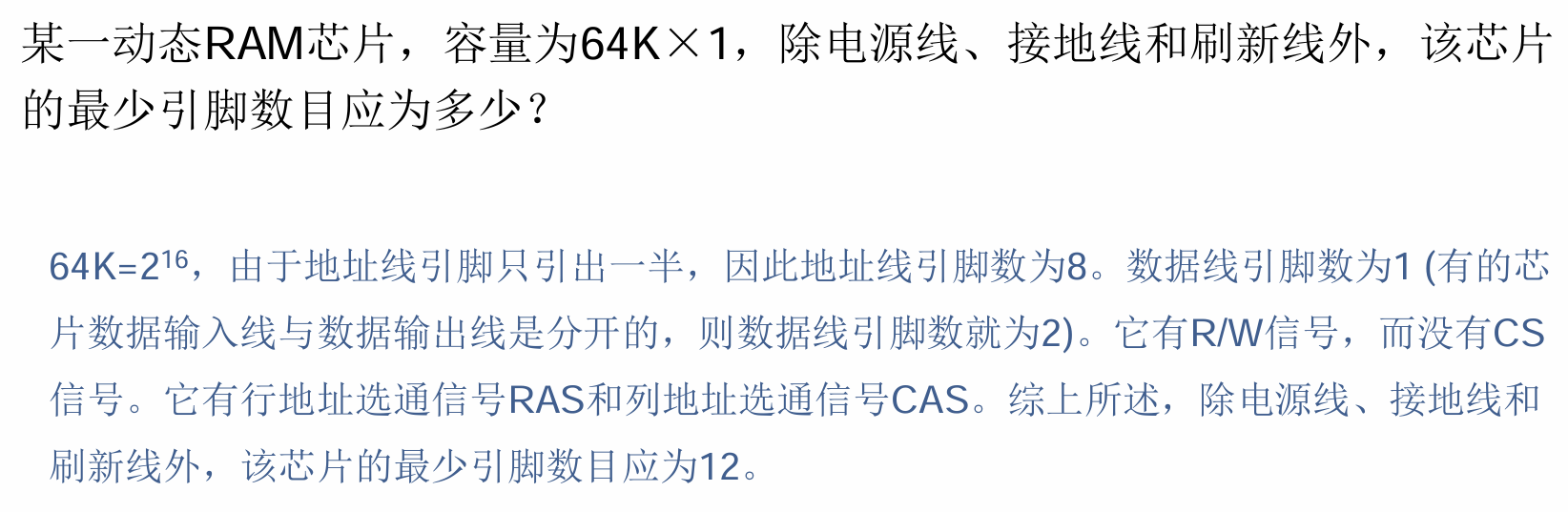

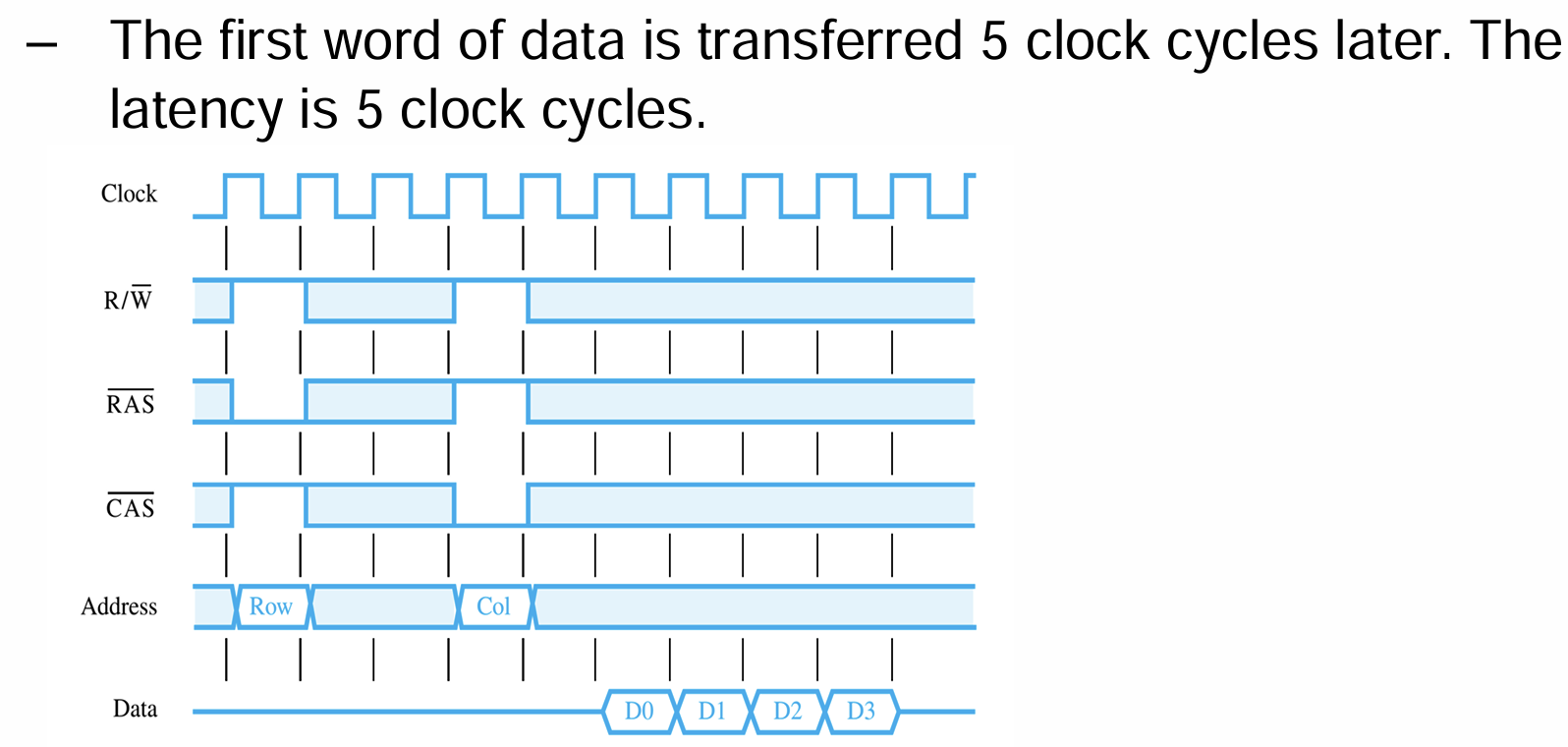

2.3 普通DRAM芯片

- 参考下图中的文字注释

- 关于引脚的复用

2.4 SDRAM

2.4.1 SDRAM原理

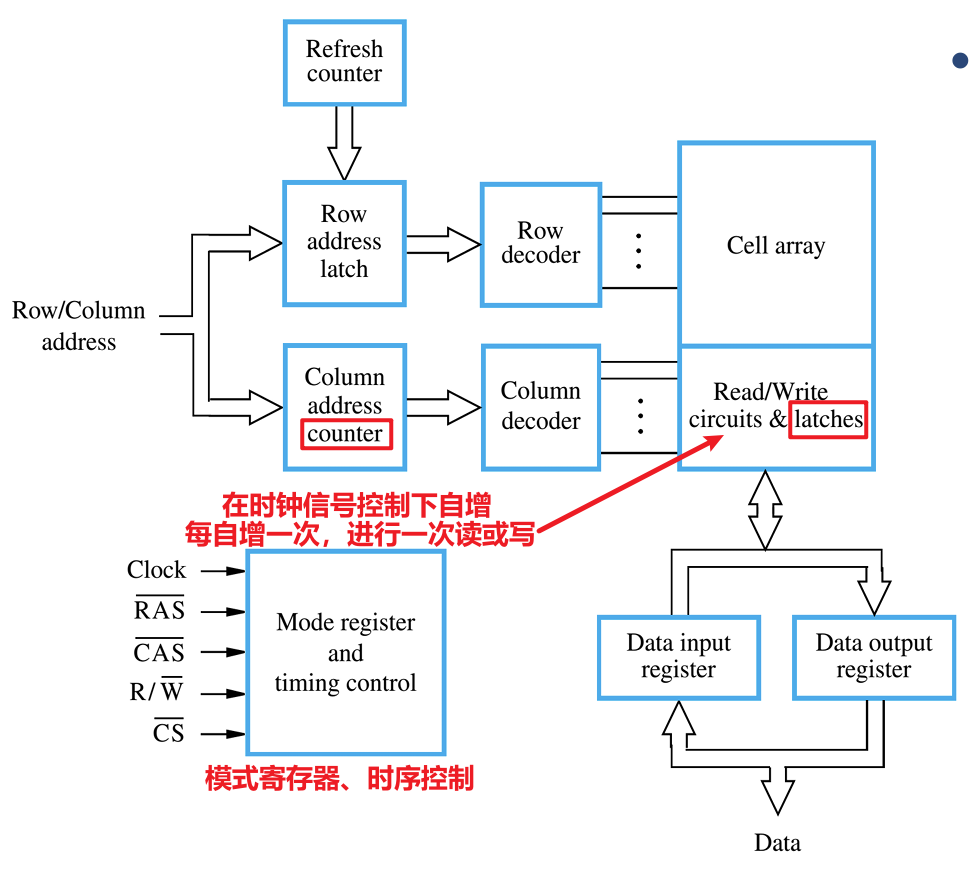

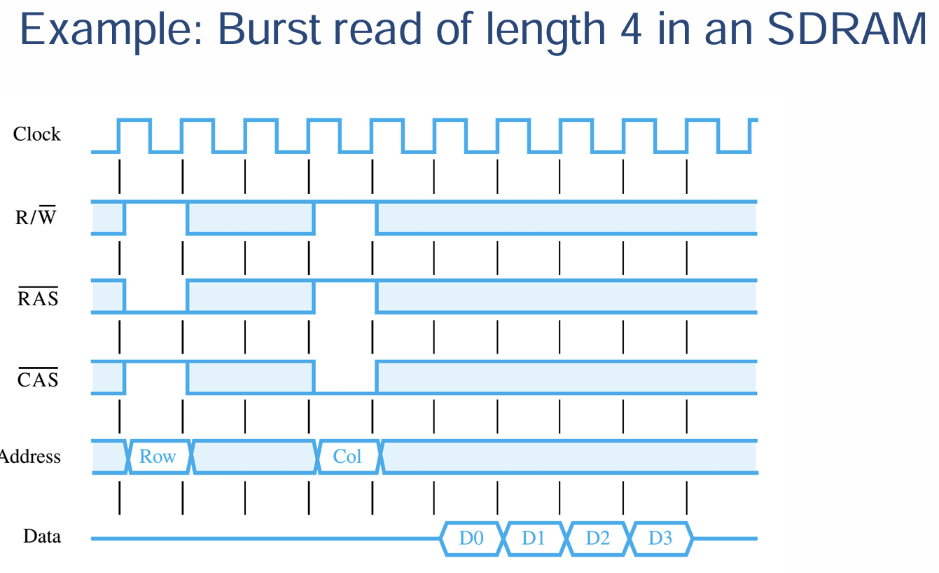

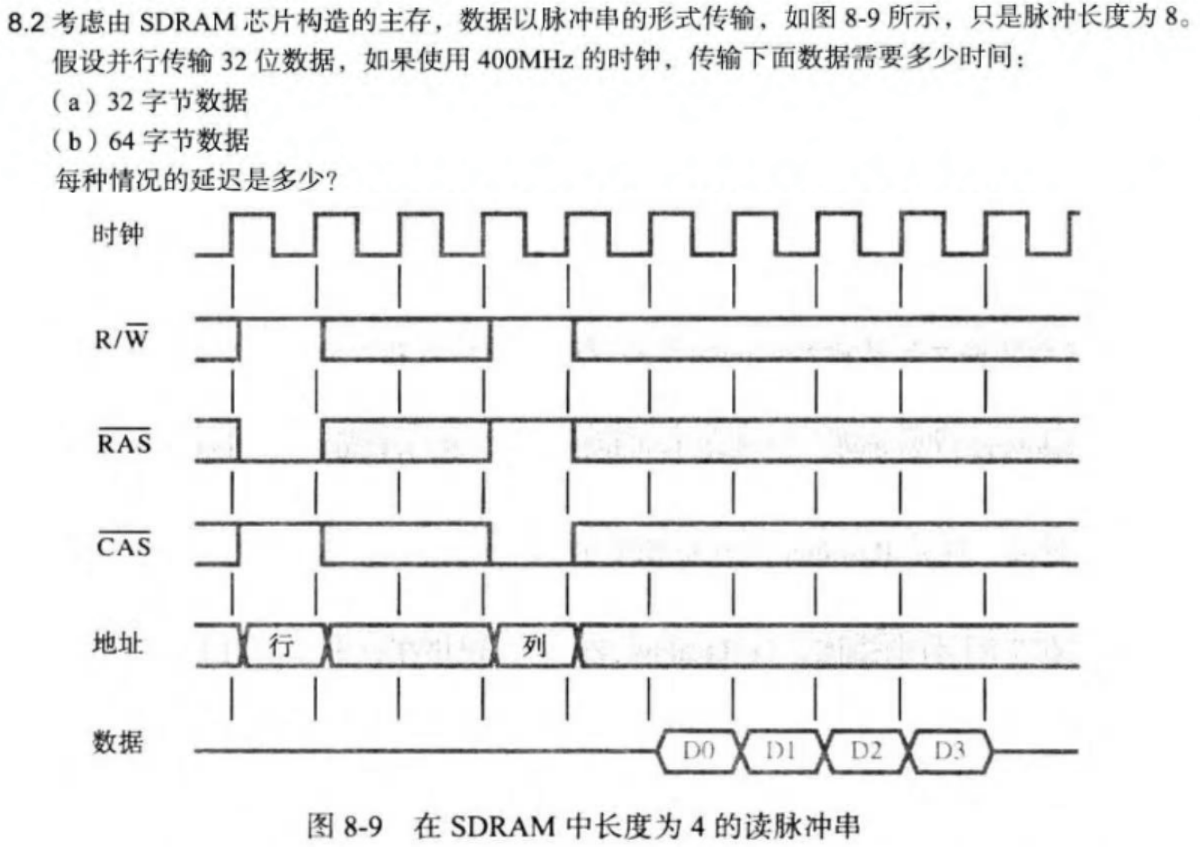

- 同步DRAM(Synchronous DRAM)简称为SDRAM,其操作基于时钟信号(Clock Signal)同步

- Burst Operation

- SDRAMs have several different modes of operation, which can be selected by writing control information into a mode register

- The burst operations use the block transfer capability

- The mode register holds a 12-bit value that the SDRAM looks at in order to determine how many columns it should BURST and in what order it should BURST them

- 衡量SDRAM性能的两个参数

- 带宽(BandWidth):每秒可以处理的数据,即可以并行(In Parallel)访问数据的速度,单位是比特每秒;存储器的带宽就是总线的带宽,即总线速度乘上其条数宽度(Effective Bandwidth = Bus Speed × Bus Width)

- 延迟(Latency):读写一个字需要的时间(In block transfers, latency is used to denote the time before it takes to transfer the first word of data)

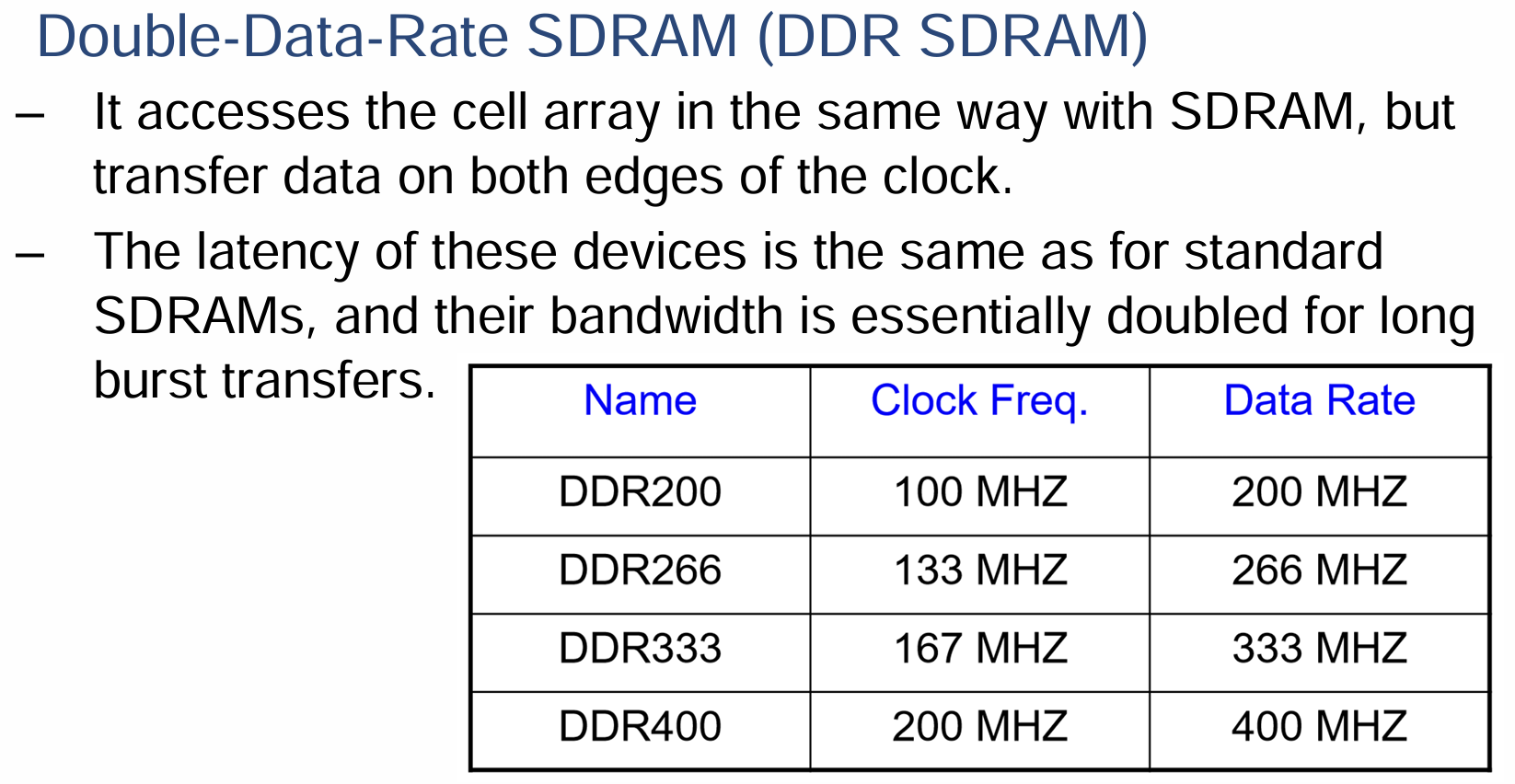

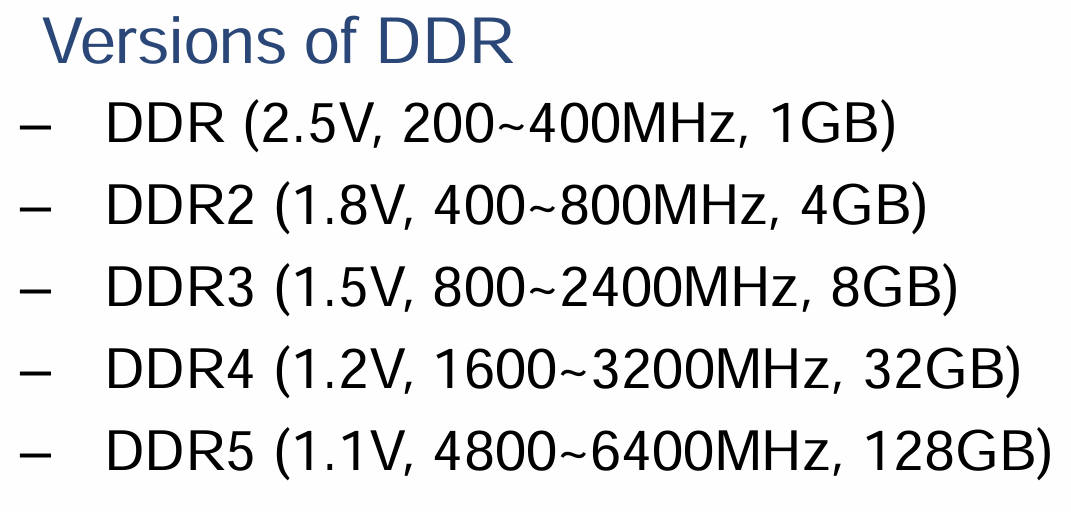

2.4.2 DDR-SDRAM

- 各版本的DDR-SDRAM(Double-Data-Rate SDRAM)及其版本差异

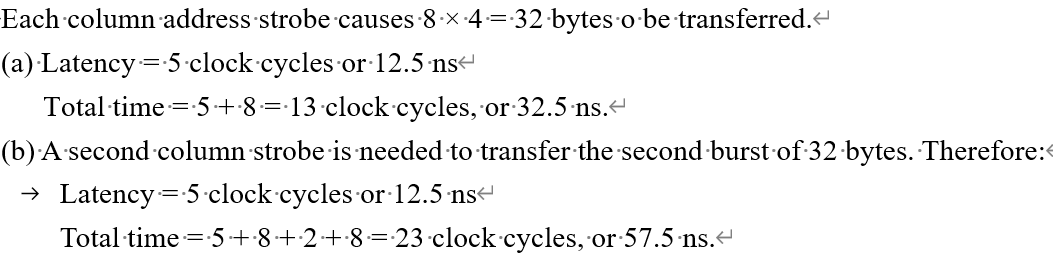

2.4.3 相关例题

三、大容量内存

3.1 静态内存系统

Static Memory System

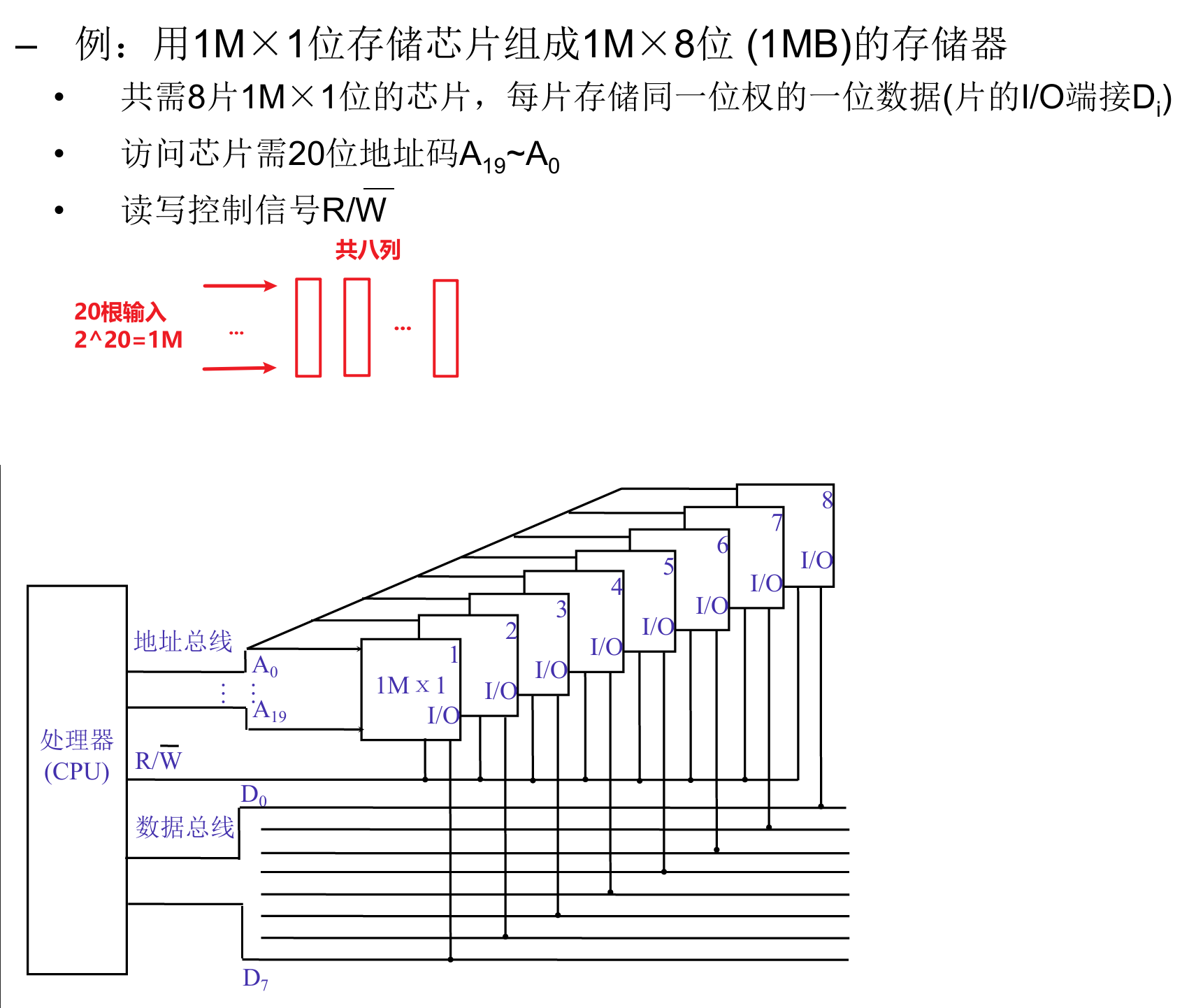

3.1.1 位扩展

- 如果单元芯片的每个存储单元的位数小于存储器字长,则需进行位扩展

3.1.2 字扩展

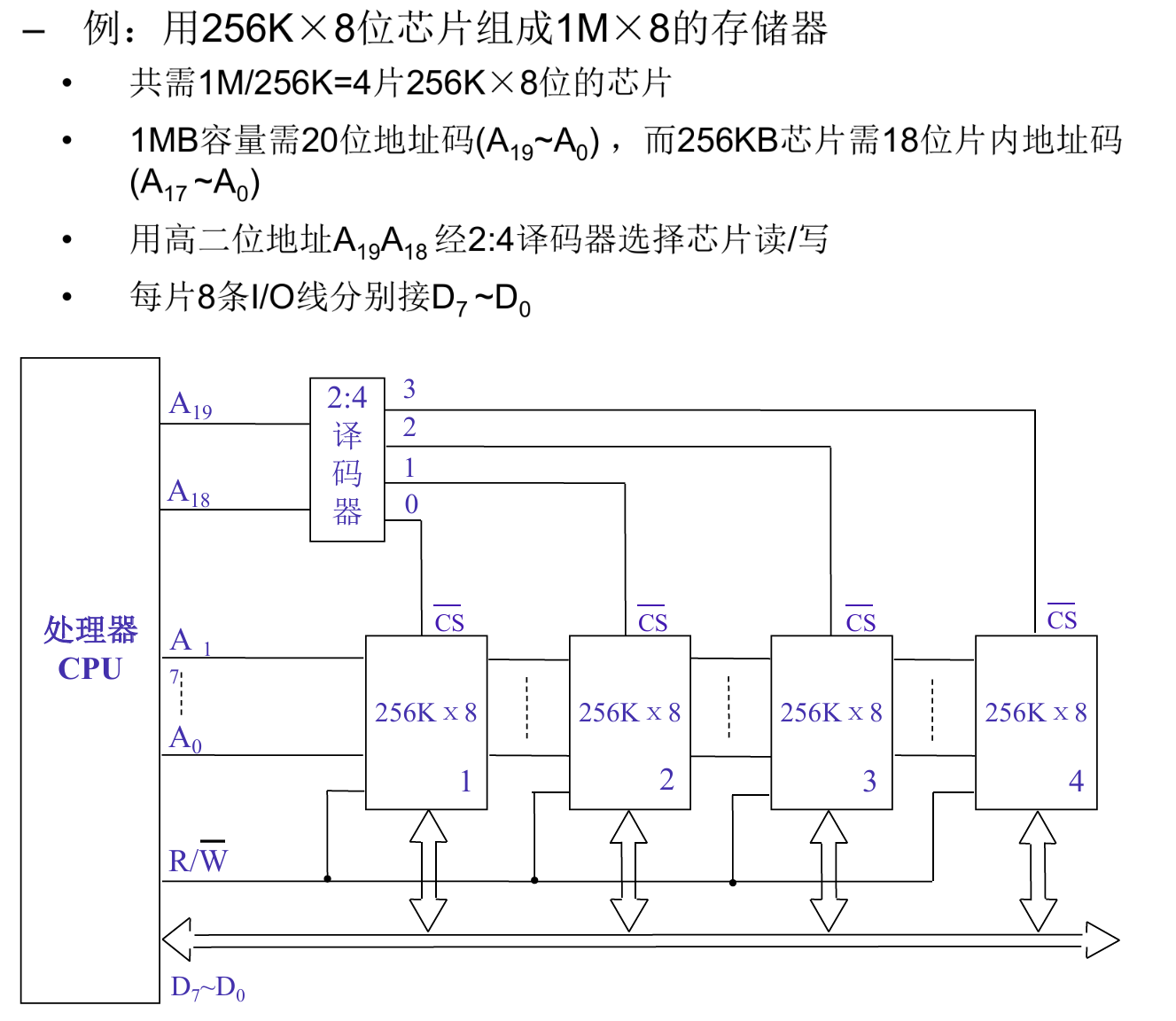

- 若芯片每个存储单元的位数等于存储器字长,但容量(字数)不够, 则需进行字扩展

3.1.3 字位同时扩展

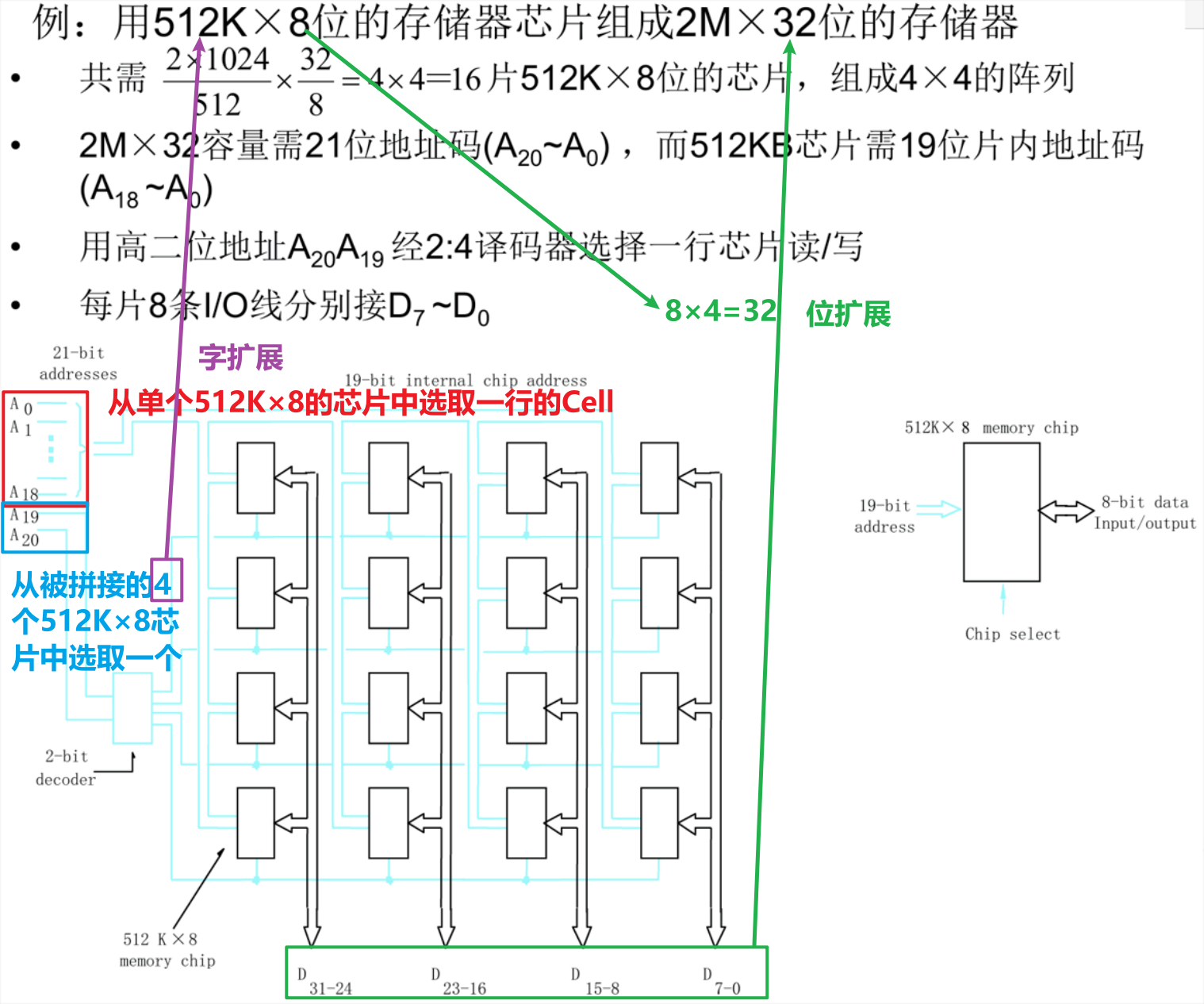

- 若单片芯片的字数和位数均小于主存的容量要求,则需同时进行字、位的扩展

- 下图中

3.1.4 总结三种方法

- 假设基本内存单元的容量为$(M×N)$比特,要用其组成$(X×Y)$比特容量的芯片则需要用到的基本内存单元的个数为$(\frac{M}{X}×\frac{N}{Y})$,其中两个除号向上取整

3.2 动态内存系统

Dynamic Memory System,其组织小容量存储器的方法和静态的大差不差,也是字、位的扩展;下面介绍两种Memory Module类型,这是一种插在电脑插槽上的内存板子

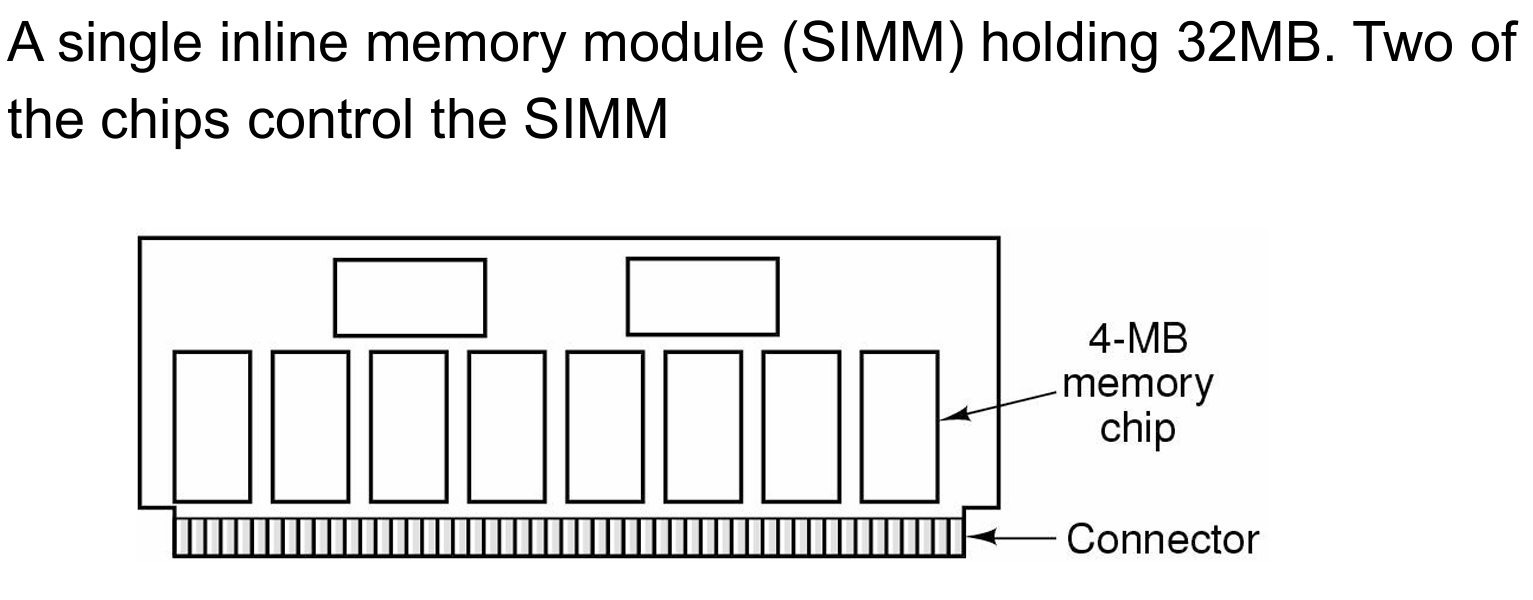

3.2.1 SIMM

Single In-line Memory Modules

- SIMM是一种打包DRAM的方法类型,适应大多数旧系统

- SIMM可以是单列的(Single-Sided,即RAM芯片只排列在一端,对称的两端引脚Connector传输信息不同),也可以是双列的(Double-Sided,即RAM芯片排列在两端,对称的两端引脚传输信息相同),下面是常见的SIMM类型(pin是引脚数)

- 30-pin SIMM:1~16MB,8bits,单端,plus 1bit for parity

- 72-pin SIMM:1、4、16MB,单端;2、8、32MB,双端;32bits,plus 4bits for parity/ECC

- SIMM的示意图如下

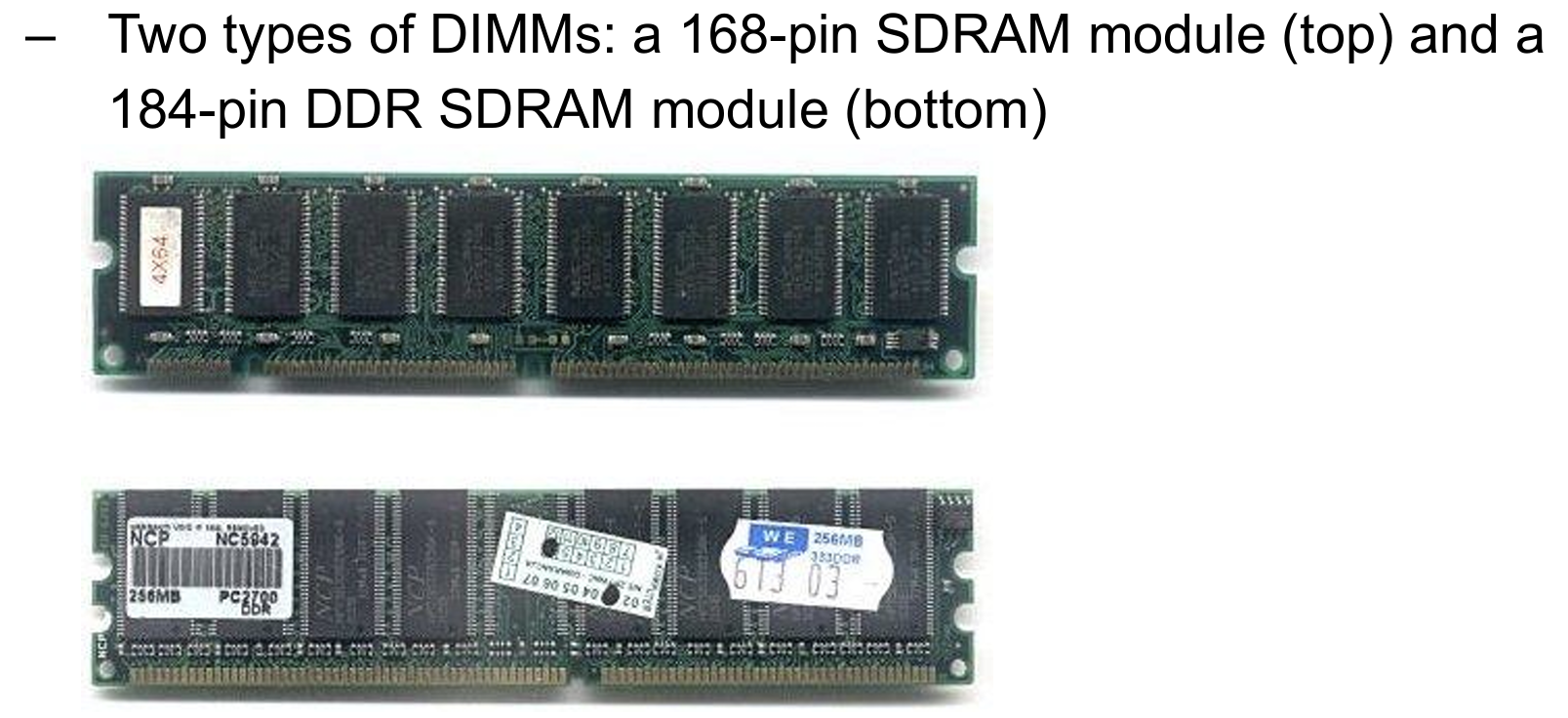

3.2.2 DIMM

Dual In-line Memory Modules

- DIMM是当前的标准内存包装方法

- DIMM能够单次传播64bits数据

- 常见的DIMM类型如下

- DIMM的示意图如下

3.3 字位扩展例题

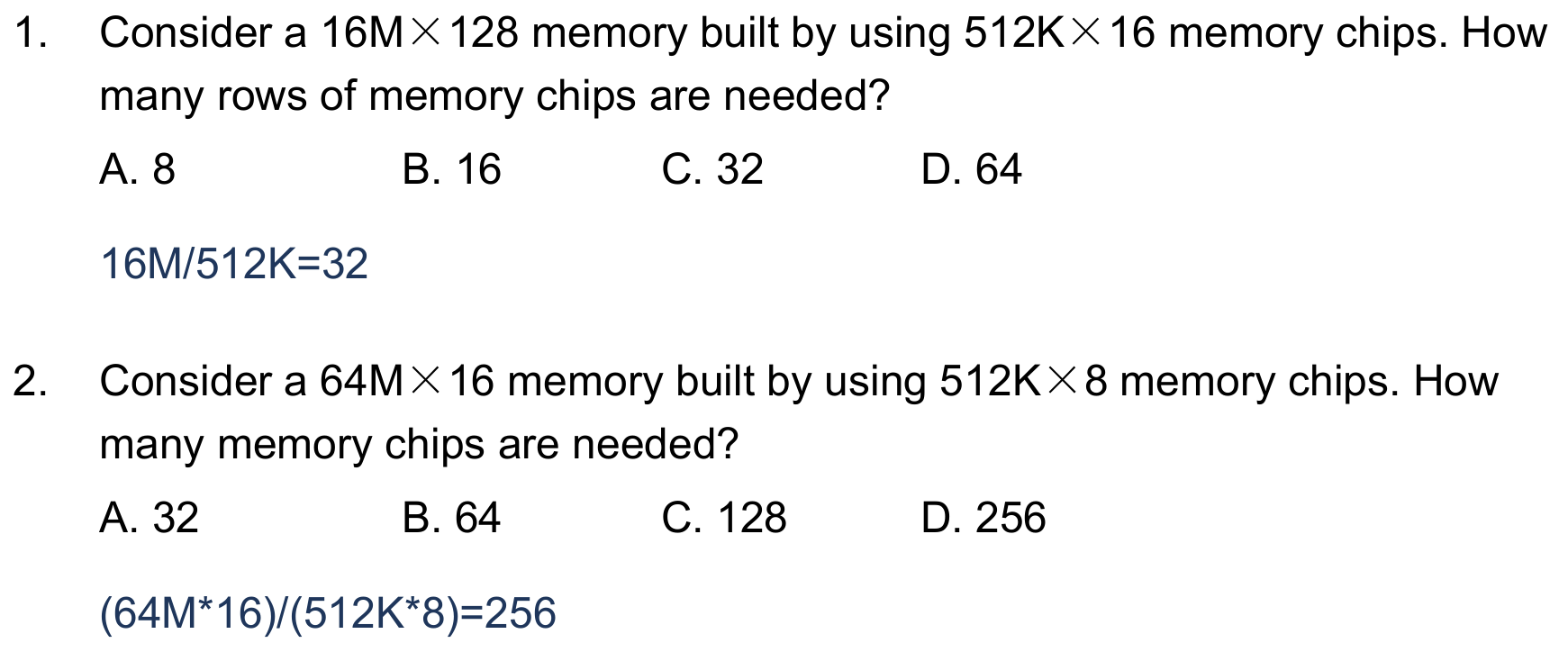

- 第一题:字数除以字数

- 第二题:字数除以字数,乘上位数除以位数

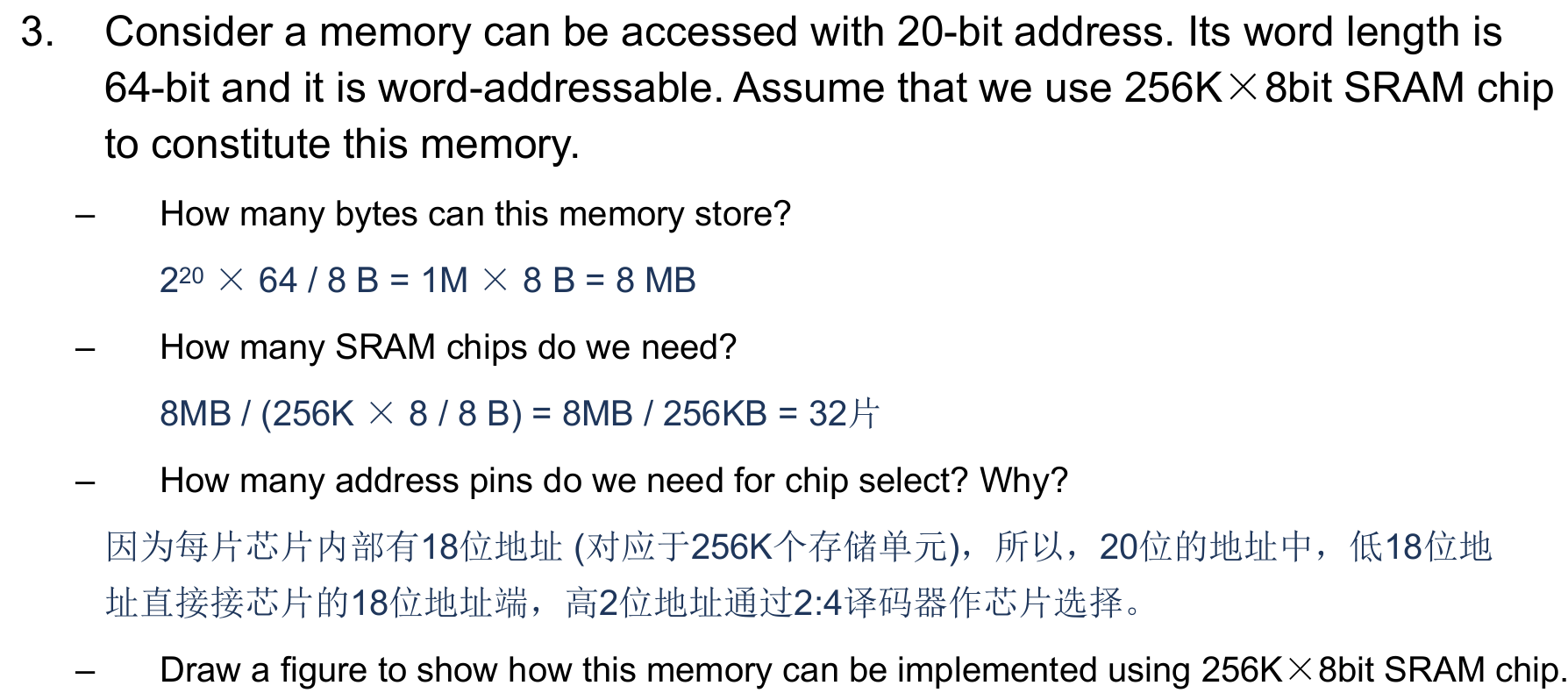

- 第三题:目标是组成$2^{20}$x64(通过20算出字数,位数已知)的存储器

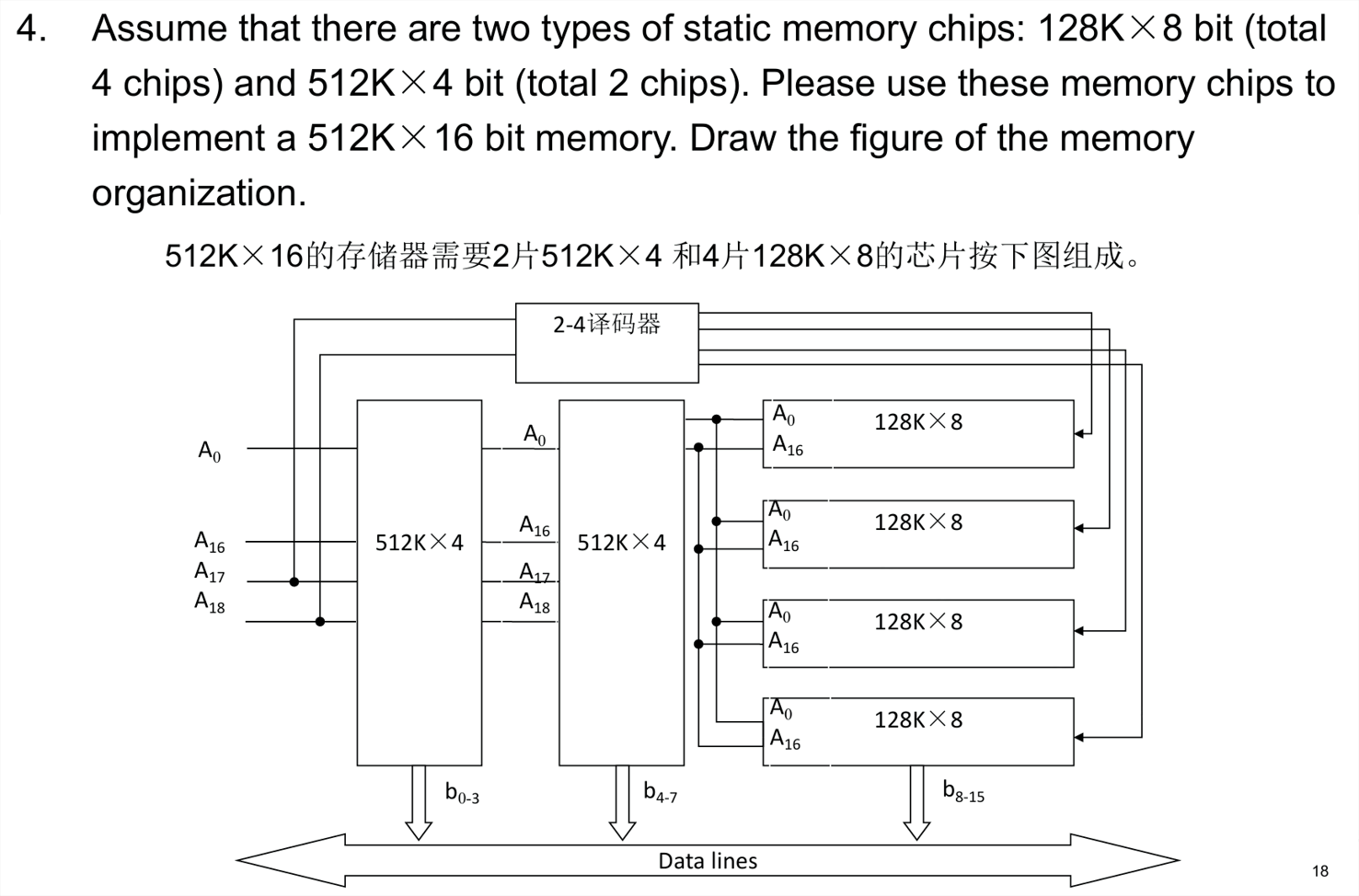

- 第四题:通过四个128Kx8bit和两个512Kx4bit芯片组成一个512Kx16bit芯片,其中译码器是对左侧19根地址导线的数据进行翻译的($512K=2^9\cdot2^{10}=2^{19}$)

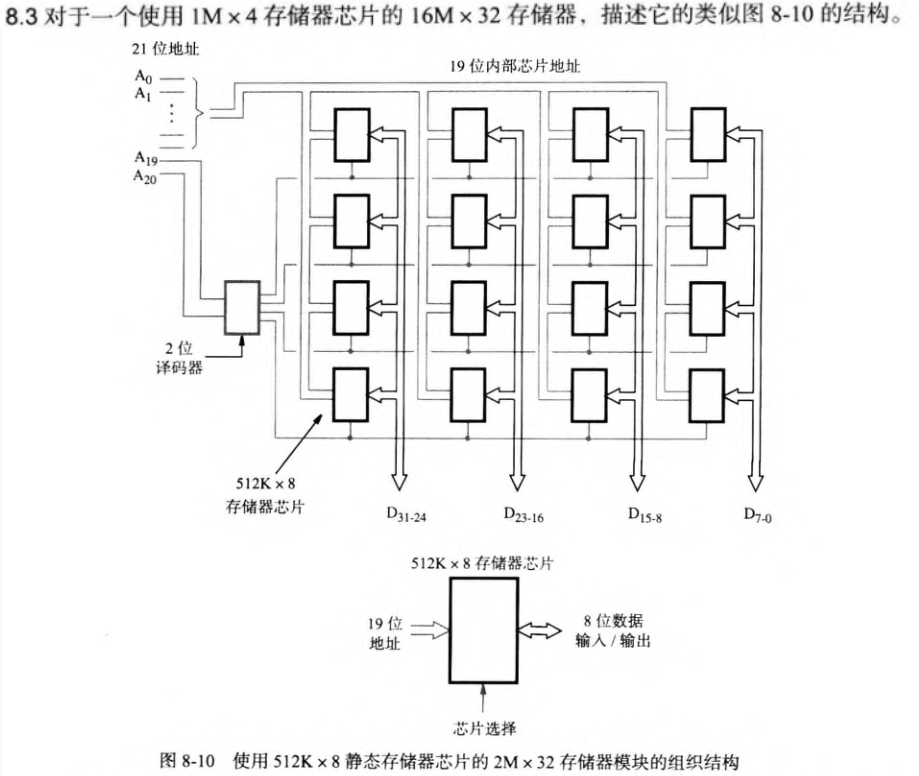

- 下面这道大题同理,不多赘述

本文由作者按照 CC BY-NC-SA 4.0 进行授权